## 700V Advanced GaNSlim Power IC NV6146C

CarbonNeutral.con

#### 1. Features

- · Integrated gate drive

- 3.3V/5V/15V PWM logic input compatible

- Programmable accurate GaN current sensing

- Over-temperature protection

- Wide V<sub>CC</sub> range (10V to 24V typical)

- Low standby current (50uA typical)

- Sleep mode current (10uA max)

- · Built-in turn-on dV/dt optimization

- Built-in turn-off di/dt optimization

- · Reliable hard and soft switching

- · Zero reverse recovery charge

#### DPAK-4L package with grounded cooling pad

- · Grounded cooling pad

- Minimized package inductance

- · Low thermal resistance

#### Sustainability

- · RoHS, Pb-free, REACH-compliant

- Up to 40% energy savings vs Si solutions

- System level 4kg CO<sub>2</sub> Carbon Footprint reduction

#### **Product Reliability**

20-year limited product warranty (see Section 15 for details)

#### 2. Applications

- · AC-DC Charger & Adapter

- Wireless power

- LED lighting

- · Solar Micro-inverters

- TV Power

- Server Power, Telecom Power

## DPAK-4L 3. Description

This feature-rich 700 V GaNSlim™ Power IC includes a high performance eMode GaN FET (170mΩ), integrated gate drive, and extended features to create the fastest, smallest, most efficient, and most robust integrated powertrain in the world.

CS

GaNSlim™ Power IC

Simplified schematic

with GaNSense <sup>™</sup> Technology

vcc

Integrated lossless current sensing eliminates external current sensing resistors and increases system efficiency, over-temperature protection increases system robustness, auto standby and sleep mode increases light/tiny/no-load efficiency.

The highest dV/dt immunity, high-speed integrated drive and industry-standard low-profile, low-inductance, DPAK package combine to enable designers to exploit Navitas GaN technology with simple, quick, reliable solutions achieving breakthrough power density and efficiency.

Navitas' GaNSlim™ power ICs extend the capabilities of traditional topologies and enable the commercial introduction of breakthrough designs.

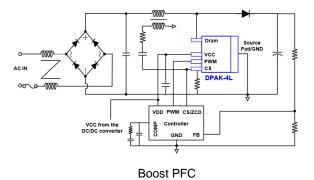

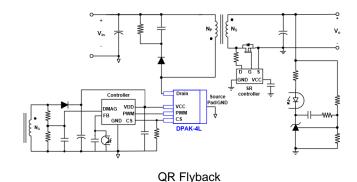

## 4. Typical Application Circuits

Final Datasheet 1 Rev Dec 05, 2024

### 5. Table of Contents

| 1. Features                                                                   | 1  |

|-------------------------------------------------------------------------------|----|

| 2. Applications                                                               | 1  |

| 3. Description                                                                | 1  |

| 4. Typical Application Circuits                                               | 1  |

| 5. Table of Contents                                                          | 2  |

| 6. Block Diagram                                                              | 3  |

| 7. Specifications                                                             | 4  |

| 7.1. Absolute Maximum Ratings (1) (with respect to Source (pad) unless noted) | 4  |

| 7.2. Recommended Operating Conditions                                         | 4  |

| 7.3. ESD Ratings                                                              | 4  |

| 7.4. Thermal Resistance                                                       | 4  |

| 7.5. Electrical Characteristics                                               | 5  |

| 7.6. Typical Waveforms                                                        | 7  |

| 8. Pin Configurations and Functions                                           | 10 |

| 8.1. GaNSlim "Single" DPAK-4L                                                 | 10 |

| 9. Functional Description                                                     | 11 |

| 9.1. GaN Power IC Connections and Component Values                            | 11 |

| 9.2. UVLO Mode                                                                | 12 |

| 9.3. Normal Operating Mode                                                    | 12 |

| 9.4. Low Power Standby Mode and Sleep Mode                                    | 13 |

| 9.5. GaNSenseTM Technology Loss-Less Current Sensing                          | 14 |

| 9.6. Over Temperature Protection (OTP)                                        | 16 |

| 9.7. Drain-to-Source Voltage Considerations                                   | 16 |

| 9.8. GaNSlim For High Side Application                                        | 17 |

| 10. PCB Layout Guidelines                                                     | 18 |

| 11. Package outline                                                           | 20 |

| 12. Tape and Reel Dimensions                                                  | 22 |

| 13. Ordering Information                                                      | 23 |

| 14. Revision History                                                          | 24 |

| 15. 20-Vear Limited Product Warranty                                          | 24 |

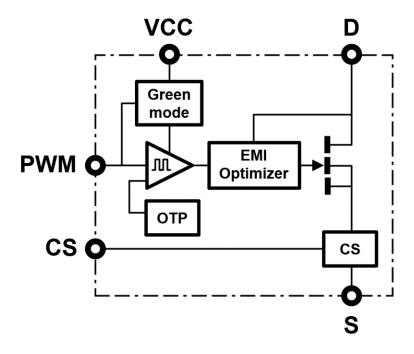

## 6. Block Diagram

#### Notes:

- GND connection for the IC is to the die pad.

- CS is the analog test output.

Final Datasheet 3 Rev Dec 05, 2024

## 7. Specifications

## 7.1. Absolute Maximum Ratings (1) (with respect to Source (pad) unless noted)

| SYMBOL               | PARAMETER                                                              | MAX        | UNITS |

|----------------------|------------------------------------------------------------------------|------------|-------|

| V <sub>DS</sub>      | Drain-to-Source Voltage                                                | -7 to +700 | V     |

| $V_{TDS}$            | Transient Drain-to-Source Voltage <sup>(2)</sup>                       | 800        | V     |

| V <sub>cc</sub>      | Supply Voltage                                                         | 30         | V     |

| V <sub>CS</sub>      | CS Pin Voltage                                                         | 5.3        | V     |

| PWM                  | OUTH Output Pin Voltage                                                | -0.6V~Vcc  | V     |

| I <sub>D</sub>       | $I_D$ 170 mΩ Version Continuous Drain Current (@ $T_C$ = 25°C)         |            | А     |

| I <sub>D</sub>       | $I_D$ 170 mΩ Version Continuous Drain Current (@ $T_C$ = 100°C)        |            | А     |

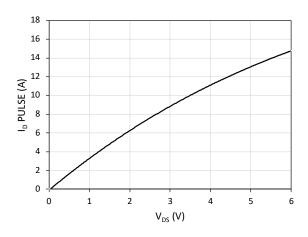

| I <sub>D</sub> PULSE | $I_D$ PULSE 170 mΩ Version Pulsed Drain Current (10 µs, $T_J$ = 125°C) |            | А     |

| T <sub>J</sub>       | T <sub>J</sub> Operating Junction Temperature                          |            | °C    |

| T <sub>STOR</sub>    | Storage Temperature                                                    | -55 to 150 | °C    |

<sup>(1)</sup> Absolute maximum ratings are stress ratings; devices subjected to stresses beyond these ratings may cause permanent damage.

## 7.2. Recommended Operating Conditions

| SYMBOL          | PARAMETER             | MIN  | TYP | MAX | UNITS |

|-----------------|-----------------------|------|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage        | 10.5 |     | 24  | V     |

| VPWM            | PWM input pin voltage | 0    | 5   | Vcc | V     |

## 7.3. ESD Ratings

| SYMBOL | PARAMETER                         | MAX   | UNITS |

|--------|-----------------------------------|-------|-------|

| HBM    | Human Body Model (per JS-001)     | 1,500 | V     |

| CDM    | Charged Device Model (per JS-002) | 1,000 | V     |

#### 7.4. Thermal Resistance

| SYMBOL PARAMETER                |                     | TYP (330 mΩ) | UNITS |

|---------------------------------|---------------------|--------------|-------|

| R <sub>eJC</sub> (1)            | Junction-to-Case    | 5.84         | °C/W  |

| R <sub>eJA</sub> <sup>(1)</sup> | Junction-to-Ambient | 49.10        | °C/W  |

<sup>(1)</sup> R<sub>o</sub> measured on DUT mounted on 1 square inch 2 oz Cu (FR4 PCB)

Final Datasheet 4 Rev Dec 05, 2024

<sup>(2)</sup> V<sub>DS (TRAN)</sub> rating allows for surge ratings during non-repetitive events that are <100us (for example start-up, line interruption). V<sub>DS (TRAN)</sub> rating allows for repetitive events that are <400ns, with 80% derating required (for example repetitive leakage inductance spikes). Refer to Section 9.7 for detailed recommended design guidelines.</p>

### 7.5. Electrical Characteristics

Typical conditions:  $V_{DS} = 400 \text{ V}$ ,  $V_{CC} = 15 \text{ V}$ ,  $T_{AMB} = 25 \text{ }^{\circ}\text{C}$ ,  $I_{D} = I_{TEST}^{(2)}$  (unless otherwise specified)

| SYMBOL                                                     | PARAMETER                                                                                                  | MIN      | TYP       | MAX     | UNITS | CONDITIONS                                                  |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------|-----------|---------|-------|-------------------------------------------------------------|--|

| V <sub>CC</sub> and V <sub>DD</sub> Supply Characteristics |                                                                                                            |          |           |         |       |                                                             |  |

| $V_{\text{CCUV+}}$                                         | V <sub>cc</sub> UVLO Rising Turn-On Threshold                                                              |          | 9         |         | V     |                                                             |  |

| V <sub>CCUV</sub> -                                        | V <sub>cc</sub> UVLO Falling Turn-Off Threshold                                                            |          |           | 6.2     | V     |                                                             |  |

| I <sub>QCC-STBY</sub>                                      | V <sub>cc</sub> Standby Current                                                                            |          | 50        |         | μΑ    | Standby                                                     |  |

| I <sub>cco</sub>                                           | V <sub>CC</sub> Operating Current                                                                          |          | 500       |         | μΑ    | PWM high                                                    |  |

| I <sub>STARTUP</sub>                                       |                                                                                                            |          |           | 10      | μΑ    | $V_{CC} = 24V$                                              |  |

| t <sub>WAKE_UV</sub> <sup>(1)</sup>                        | Wake Up Delay from UVLO Mode                                                                               |          | 35        |         | μs    | $V_{CC} = 0 \rightarrow 15V$ during 1µs PWM tie to $V_{CC}$ |  |

| I <sub>CC-SW</sub>                                         | $V_{CC}$ Switching Current, 170 m $\Omega$                                                                 |          | 1         |         | mA    | $F_{SW} = 500 \text{kHz}, V_{DS} = \text{Open}$             |  |

|                                                            | Input Charac                                                                                               | teristic | s (PWM    | pin)    |       |                                                             |  |

| $V_{\text{PWM\_H}}$                                        | PWM Pin Logic High Threshold                                                                               |          |           | 2.7     | V     |                                                             |  |

| $V_{\text{PWM\_L}}$                                        | PWM Pin Logic Low Threshold                                                                                | 1.1      |           |         | V     |                                                             |  |

| V <sub>PWM-HYS</sub>                                       | PWM Pin Input Logic Hysteresis                                                                             |          | 0.6       |         | V     |                                                             |  |

|                                                            | Sleep mod                                                                                                  | le Chara | cteristic | s       |       |                                                             |  |

| t <sub>WAKE_Sleep</sub>                                    | Wake up delay time from Sleep mode                                                                         |          |           | 1.1     | us    | From PWM high                                               |  |

| t <sub>TO_Sleep</sub>                                      | Time Out Delay Entering Sleep Mode                                                                         |          | 11        |         | ms    | From PWM low                                                |  |

|                                                            | Standby Mo                                                                                                 | de Cha   | racterist | ics     | •     |                                                             |  |

| t <sub>TO_STBY</sub>                                       | Time Out Delay Entering Standby Mode                                                                       |          | 75        |         | μs    |                                                             |  |

| t <sub>WAKE_STBY</sub>                                     | Wake Up Delay Time from Standby Mode                                                                       |          |           | 350     | ns    |                                                             |  |

|                                                            | Current Sense C                                                                                            | haracte  | ristics ( | CS pin) |       |                                                             |  |

| I <sub>CS</sub>                                            | CS Pin Output Current                                                                                      | 1.16     | 1.25      | 1.34    | mA    | $V_{PWM} = 5V, I_{DS} = .5*I_{DSMAX}$                       |  |

| t <sub>CSDLY10</sub> <sup>(1)</sup>                        | CS Pin Delay from I <sub>DS</sub> =10% rated current to V <sub>CS</sub> =10% of desired full-scale voltage |          | 62        |         | ns    | 0.25us from 0 to Idmax<br>R <sub>CS</sub> =400Ohm           |  |

Final Datasheet 5 Rev Dec 05, 2024

Typical conditions:  $V_{DS} = 400 \text{ V}$ ,  $V_{CC} = 15 \text{ V}$ ,  $T_{AMB} = 25 \text{ }^{\circ}\text{C}$ ,  $I_{D} = I_{TEST}^{(2)}$  (unless otherwise specified)

| SYMBOL                | PARAMETER                      |  | TYP | MAX | UNITS | CONDITIONS |

|-----------------------|--------------------------------|--|-----|-----|-------|------------|

|                       | Over Temperature Protection    |  |     |     |       |            |

| T <sub>OTP+</sub> (1) | OTP Shutdown Threshold         |  | 160 |     | °C    |            |

| T <sub>OTP_HYS</sub>  | OTP_HYS OTP Restart Hysteresis |  | 65  |     | °C    |            |

## **Electrical Characteristics (cont.)**

Typical conditions:  $V_{DS} = 400 \text{ V}$ ,  $V_{CC} = 15 \text{ V}$ ,  $T_{AMB} = 25 \text{ }^{\circ}\text{C}$ ,  $I_{D} = I_{TEST}^{(2)}$  (unless otherwise specified)

| SYMBOL                                                                      | PARAMETER                                        |  | TYP  | MAX | UNITS | CONDITIONS                                                                        |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------|--|------|-----|-------|-----------------------------------------------------------------------------------|--|--|

|                                                                             | NV6146C GaN FET Characteristics (170 mΩ version) |  |      |     |       |                                                                                   |  |  |

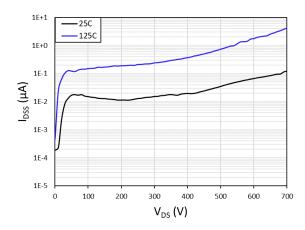

| I <sub>DSS</sub>                                                            | Drain-Source Leakage Current                     |  | 0.15 | 25  | μΑ    | $V_{DS} = 650 \text{ V}, V_{PWM} = 0 \text{ V}$                                   |  |  |

| I <sub>DSS</sub>                                                            | I <sub>DSS</sub> Drain-Source Leakage Current    |  | 11   |     | μΑ    | $V_{DS} = 650 \text{ V}, V_{PWM} = 0 \text{ V},$ $T_{C} = 150 {}^{\circ}\text{C}$ |  |  |

| R <sub>DS(ON)</sub>                                                         | Drain-Source Resistance                          |  | 170  | 238 | mΩ    | $V_{PWM} = 5 \text{ V}, I_D = 4 \text{ A}$                                        |  |  |

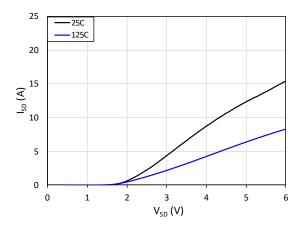

| V <sub>SD</sub>                                                             | Source-Drain Reverse Voltage                     |  | 3.5  | 5   | V     | $V_{PWM} = 0 \text{ V, } I_{SD} = 4 \text{ A}$                                    |  |  |

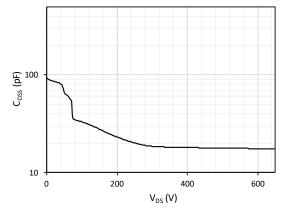

| Qoss                                                                        | Output Charge                                    |  | 13.5 |     | nC    | $V_{DS} = 400 \text{ V}, V_{PWM} = 0 \text{ V}$                                   |  |  |

| $Q_{_{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | Reverse Recovery Charge                          |  | 0    |     | nC    |                                                                                   |  |  |

| Coss                                                                        | Output Capacitance                               |  | 18   |     | pF    | V <sub>DS</sub> = 400 V, V <sub>PWM</sub> = 0 V                                   |  |  |

| C <sub>O(er)</sub> (2)                                                      | Effective Output Capacitance, Energy Related     |  | 23   |     | pF    | $V_{DS} = 400 \text{ V}, V_{PWM} = 0 \text{ V}$                                   |  |  |

| C <sub>O(tr)</sub> (3)                                                      | Effective Output Capacitance, Time Related       |  | 33   |     | pF    | $V_{DS} = 400 \text{ V}, V_{PWM} = 0 \text{ V}$                                   |  |  |

<sup>(1)</sup> Guarantee by design

Final Datasheet 6 Rev Dec 05, 2024

<sup>(2)</sup>  $I_{TEST} = 2A$

<sup>(3)</sup>  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

<sup>(4)</sup>  $C_{O(sr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

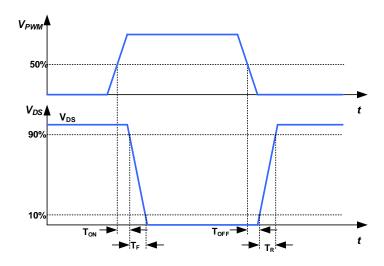

## 7.6. Typical Waveforms

(T<sub>C</sub> = 25 °C unless otherwise specified)

Figure 1. Inductive Switching Test Circuit

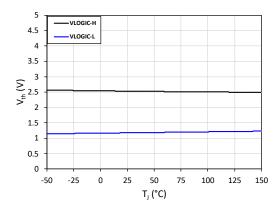

Figure 2.  $V_{\text{LOGIC-H}}$  and  $V_{\text{LOGIC-L}}$  vs.

junction temperature(T\_I)

T<sub>J</sub> (°C)

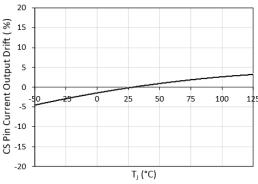

Figure 4. CS Pin Current Output Drift

vs. case temperature (Tc)

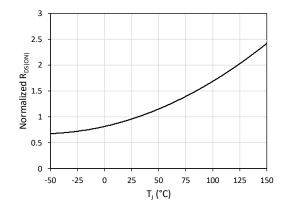

Figure 3. Normalized on-resistance  $(R_{DS(ON)})$  vs. junction temperature  $(T_j)$

#### **Typical Waveform**

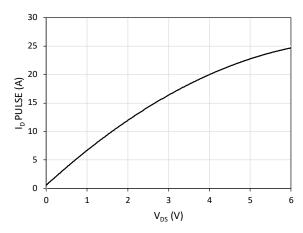

Figure 5. Pulsed Drain current (I<sub>D</sub> PULSE) vs. drain-to-source voltage (V<sub>DS</sub>) at T = 25 °C

Figure 7. Source-to-drain reverse conduction voltage

Figure 9. Output capacitance ( $C_{OSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

Figure 6. Pulsed Drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at T = 125 °C

Figure 8. Drain-to-source leakage current ( $I_{DSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

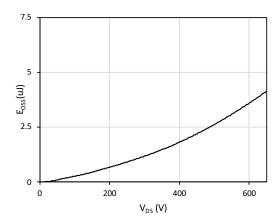

Figure 10. Energy stored in output capacitance  $(E_{OSS})$  vs. drain-to-source voltage  $(V_{DS})$

#### Typical Waveform(cont.)

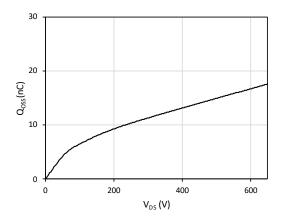

Figure 11. Charge stored in output capacitance ( $Q_{OSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

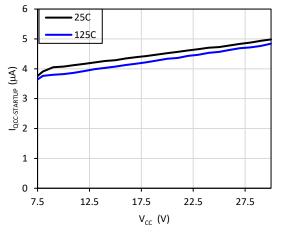

Figure 13. VCC startup current (IQCC-startup) vs. Supply Voltage (VCC)

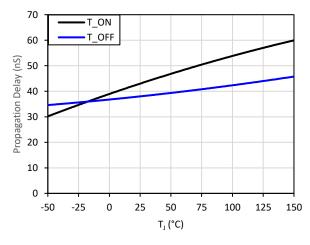

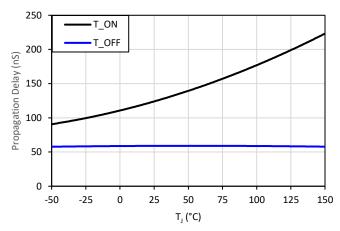

Figure 15. CP01 Propagation delay (TON and TOFF) vs. junction temperature(TJ)

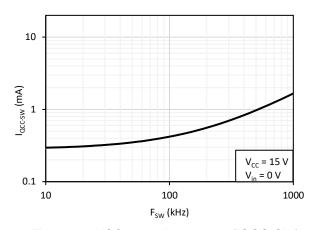

Figure 12. VCC operating current (IQCC-SW) vs. switching frequency

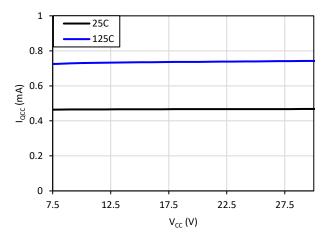

Figure 14. VCC quiescent current vs. Supply Voltage (VCC)

Figure 16. CQ01 Propagation delay (TON and TOFF) vs. junction temperature(TJ)

## 8. Pin Configurations and Functions

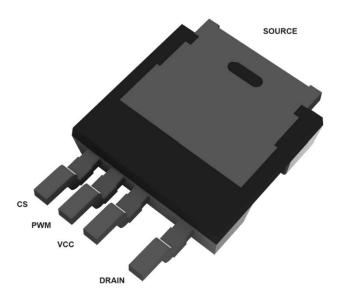

## 8.1. GaNSlim "Single" DPAK-4L

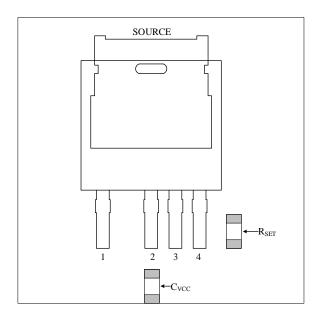

Figure 17. Package Bottom View

| Pin    |        | I/O <sup>(1)</sup> | December                                                                                                                                                 |

|--------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Symbol | 1/0(1)             | Description                                                                                                                                              |

| 1      | Drain  | Р                  | Drain of power FET.                                                                                                                                      |

| 2      | VCC    | Р                  | IC supply voltage.                                                                                                                                       |

| 3      | PWM    | I                  | PWM input.                                                                                                                                               |

| 4      | CS     | 0                  | GaN FET I DS current sensing set pin. Internal current source and external resistor sets current measurement level. External resistor reference is SGND. |

| SOURCE | GND    | G                  | Source of power FET & IC supply ground. Metal pad on bottom of package.                                                                                  |

Note 1: I = Input, O = Output, P = Power, G = Ground, T = Test Mode

Final Datasheet 10 Rev Dec 05, 2024

## 9. Functional Description

The following functional description contains additional information regarding the IC operating modes and pin functionality. Please refer to the State Diagram for additional details.

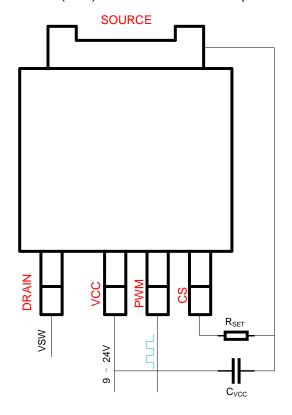

#### 9.1. GaN Power IC Connections and Component Values

The typical connection diagram for this GaN Power IC is shown in Figure 18. The IC pins include drain of the GaN power FET (D), source of the GaN power FET (S), IC supply ( $V_{CC}$ ), PWM input (PWM), and current sensing output (CS). The external components around the IC include  $V_{CC}$  filter capacitor ( $C_{VCC}$ ) connected between  $V_{CC}$  pin and S pin, a current sense amplitude set resistor ( $R_{SET}$ ) connected between CS pin and S.

Figure 18. IC connection diagram

The following table (Table I) shows the recommended component values (typical only) for the external components connected to the pins of this GaN power IC. These components should be placed as close as possible to the IC. Please see PCB Layout Guidelines for more information.

| SYM              | DESCRIPTION                          | ТҮР                                                      | UNITS |

|------------------|--------------------------------------|----------------------------------------------------------|-------|

| C <sub>VCC</sub> | V <sub>CC</sub> supply capacitor     | 0.1                                                      | μF    |

| R <sub>SET</sub> | Current sense amplitude set resistor | Depends on system design (See<br>Section 9.5 Equation 1) | Ω     |

Table I. Recommended component values (typical only).

Final Datasheet 11 Rev Dec 05, 2024

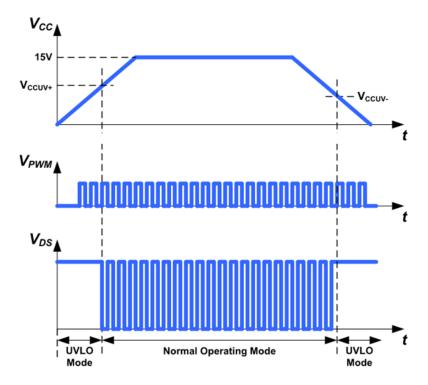

#### 9.2. UVLO Mode

This GaN Power IC includes under-voltage lockout (UVLO) circuits for properly disabling all the internal circuitry when VCC is below the VCCUV+ threshold (8.5V, typical). During UVLO Mode, the internal gate drive and power FET are disabled and VCC consumes a low quiescent current which is less than 10uA. As the VCC supply voltage increases (Figure 19) and exceeds VCCUV+, the IC enters Normal Operating Mode when PWM goes high. The gate drive is enabled and the control signal at the PWM input turns the internal GaN power FET on and off normally. During system power off, when VCC decreases below the VCCUV- threshold (5.5, typical), the gate drive is disabled and the IC enters UVLO Mode.

Figure 19. UVLO Mode and Normal Operating Mode Timing Diagram

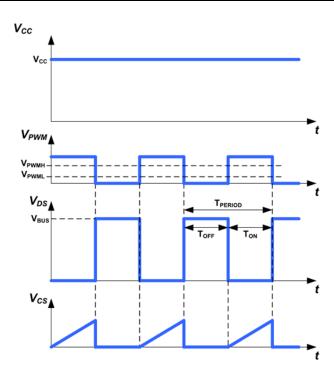

#### 9.3. Normal Operating Mode

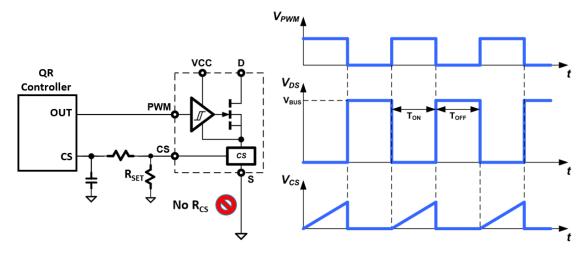

During Normal Operating Mode, all the internal circuit blocks are active. V<sub>CC</sub> is above 9.5V, the internal gate drive and power FET are both enabled. The external PWM signal at the PWM pin determines the frequency and duty-cycle of the internal gate of the power FET. As the PWM voltage toggles above and below the rising and falling input thresholds (2.7V and 1.1V), the internal power FET toggles on and off (Figure 20). The drain of the power FET then toggles between the source voltage (power ground) and a higher voltage level (700V, max), depending on the external power conversion circuit topology. During each on-time, the CS pin outputs a voltage signal from the internal loss-less current sensing circuit. This circuit measures the current flowing in the GaN power FET without the need for an external current sensing resistor (see section 9.5 GaNSense<sup>TM</sup> Technology Loss-Less Current Sensing).

Final Datasheet 12 Rev Dec 05, 2024

Figure 20. Normal Operating Mode Timing Diagram (PWM input)

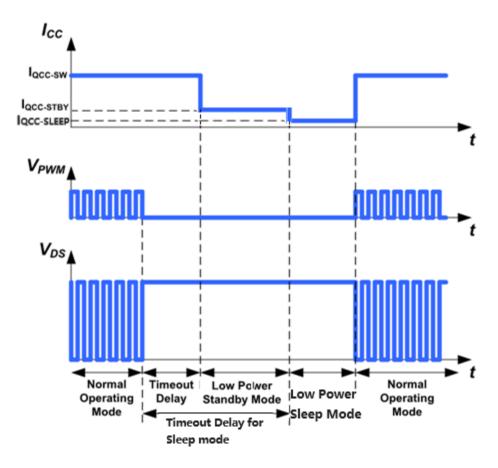

## 9.4. Low Power Standby Mode and Sleep Mode

This GaN Power IC includes an autonomous Low Power Standby Mode for disabling the IC and reducing the VCC current consumption. During Normal Operating Mode, the PWM pin toggles high and low to turn the GaN power FET on and off. If the input pulses at the PWM pin stop and stay below the lower V<sub>PWML</sub> turn-off threshold (1.1V, typical) for the duration of the internal timeout standby delay (t<sub>TO\_STBY</sub>, 75usec, typical), then the IC will automatically enter Low Power Standby Mode (Figure 21). This will disable the gate drive and internal current sense circuitry and reduce the V<sub>CC</sub> supply current to a low level (50uA, typical). If PWM pin continue to stay below the lower VPWML turn-off threshold for the duration of the internal timeout sleep delay (t<sub>TO\_SLEEP</sub>, 10msec, typical), then the IC will automatically enter Low Power Sleep Mode (Figure 21). This will disable the gate drive and other internal circuitry and reduce the V<sub>CC</sub> supply current to less than 10uA. When the PWM pulses restart, the IC will wake up with another wake-up delay (less than 200ns from standby mode or less than 1us from Sleep mode) at the first rising edge of the PWM input and enter Normal Operating Mode again.

Final Datasheet 13 Rev Dec 05, 2024

Figure 21. Sleep Mode Operating Timing Diagram

## 9.5. GaNSenseTM Technology Loss-Less Current Sensing

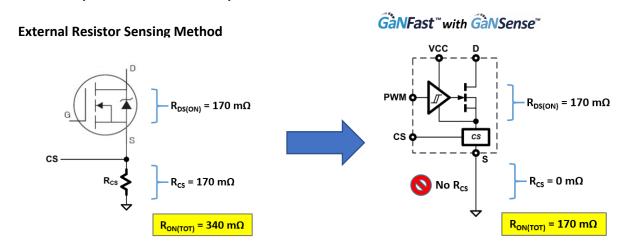

For many applications it is necessary to sense the cycle-by-cycle current flowing through the power FET. Existing current sensing solutions include placing a current sensing resistor in between the source of the power FET and PGND. This resistor method increases system conduction power losses, creates a hotspot on the PCB, and lowers overall system efficiency. To eliminate this external resistor and hotspot, and increase system efficiency, this IC includes GaNSenseTM Technology for integrated and accurate loss-less current sensing. The current flowing through the internal GaN power FET is sensed internally and then converted to a current at the current sensing output pin (CS). An external resistor (R<sub>SET</sub>) is connected from the CS pin to the GND pin and is used to set the amplitude of the CS pin voltage signal (Figure 22). This allows for the CS pin signal to programmed to work with different controllers with different current sensing input thresholds.

Final Datasheet 14 Rev Dec 05, 2024

Figure 22. Current sensing circuit and timing diagram

When comparing GaNSenseTM Technology versus existing external resistor sensing method (Figure 23), the total ON resistance,  $R_{ON(TOT)}$ , can be substantially reduced. For a 65W high-frequency QR flyback circuit, for example,  $R_{ON(TOT)}$  is reduced from 340m to 170m. The power loss savings by eliminating the external resistor results in a +0.5% efficiency benefit for the overall system.

Figure 23. External resistor sensing vs. GaNSense™ Technology

To select the correct R<sub>SET</sub> resistor value, the following equation (Equation 1) can be used. This equation uses the equivalent desired external current sensing resistor value (R<sub>CS</sub>), together with the gain of the internal sensing circuitry, to generate the equivalent R<sub>SET</sub> resistor value. This R<sub>SET</sub> value will then give the correct voltage level at the CS pin to be compatible with the internal current sensing threshold of the system controller.

$$R_{SET} * I_{CS} = R_{CS} * I_{DS}$$

$$I_{CS\_Ratio} = \frac{I_{DS}}{I_{CS}}$$

$$R_{SET} = I_{CS\_Ratio} * R_{CS}$$

Equation 1. R<sub>SET</sub> resistor value equation

| PartNumber | NV6146C |

|------------|---------|

| Ics_ratio  | 3520    |

Final Datasheet 15 Rev Dec 05, 2024

## 9.6. Over Temperature Protection (OTP)

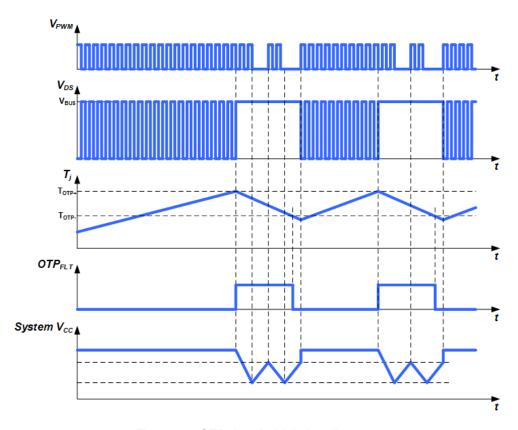

This GaN Power IC includes over-temperature detection and protection (OTP) circuitry to protect the IC against excessively high junction temperatures (T<sub>J</sub>). High junction temperatures can occur due to overload, high ambient temperatures, and/or poor thermal management. Should T<sub>J</sub> exceed the internal T<sub>OTP+</sub> threshold (165°C, typical) then the IC will latch off safely. When T<sub>J</sub> decreases again and falls below the internal T<sub>OTP-</sub> threshold (95°C, typical), then the OTP latch will be reset. Until then, internal OTP latch guaranteed to remain in the correct state while V<sub>CC</sub> is greater than 5V. During an OTP event, this GaN IC will latch off and the system V<sub>CC</sub> supply voltage will decrease due to the loss of the aux winding supply. The system V<sub>CC</sub> will fall below the lower UV- threshold of the controller and the high-voltage start-up circuit will turn-on and V<sub>CC</sub> will increase again (Figure 24). V<sub>CC</sub> will increase above the rising UV+ threshold and the controller turn on again and deliver PWM pulses again.

Figure 24. OTP threshold timing diagram

## 9.7. Drain-to-Source Voltage Considerations

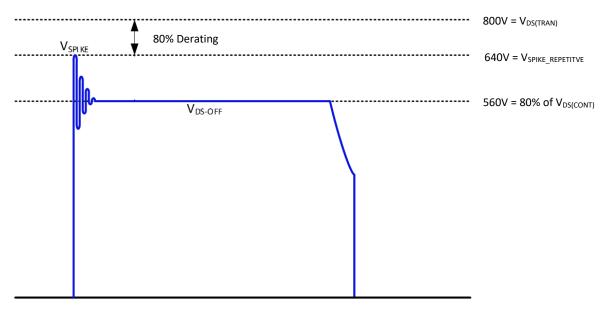

GaN Power ICs have been designed and tested to provide significant design margin to handle transient and continuous voltage conditions that are commonly seen in single-ended topologies, such as quasi-resonant (QR) flyback applications. The different voltage levels and recommended margins in a typical QR flyback can be analyzed using Figure 25. When the device is switched off, the energy stored in the transformer leakage inductance will cause VDS to overshoot to the level of VSPIKE. The clamp circuit should be designed to control the magnitude of VSPIKE. After dissipation of the leakage energy, the device VDS will settle to the level of the bus voltage plus the reflected output voltage which is defined in Figure 25 as VDS-OFF.

• For repetitive events, 80% derating should be applied from V<sub>DS (TRAN)</sub> rating (800V) to 640V max under the worst-case operating conditions.

Final Datasheet 16 Rev Dec 05, 2024

- It is recommended to design the system such that V<sub>DS-OFF</sub> is derated 80% from the V<sub>DS(CONT)</sub> (700V) max rating to 560V.

- For half-bridge based topologies, such as LLC, VDS voltage is clamped to the bus voltage. VDS should be designed such that it meets the V<sub>DS-OFF</sub> derating guideline (560V).

- Non-repetitive events are infrequent, one-time conditions such as line surge, ESD, and lightning. No derating from the VDS(TRAN) rating (800V) is needed for non-repetitive VSPIKE durations < 100 µs. The VDS(TRAN) rating (800V) allows for repetitive events that are <400ns, with 80% derating required (for example repetitive leakage inductance spikes).

Figure 25. QR flyback drain-to-source voltage stress diagram

## 9.8. GaNSlim For High Side Application

The wake-up time from UVLO model of GaNSlim has 35us (typ) delay, so when GanSlim is designed for high side application, it requires the controller to accommodate. Navitas apps team has validated that GaNSlim works well with some controllers. It's highly recommended that the application note AN031 is referred to for system design if GaNSlim is used for high side.

**Final Datasheet** 17 Rev Dec 05, 2024

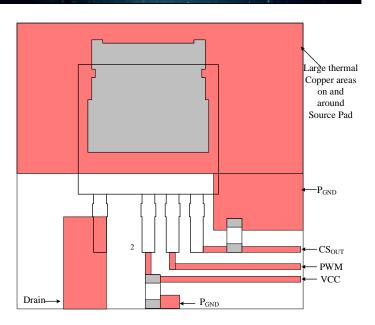

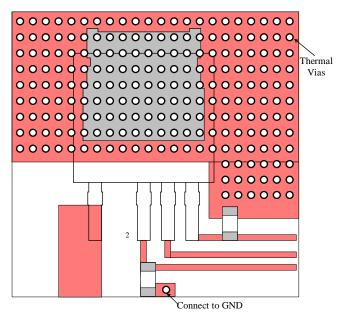

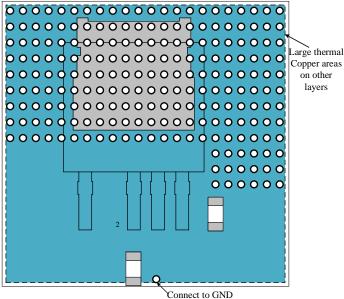

#### 10. PCB Layout Guidelines

The design of the PCB layout is critical for good noise immunity, sufficient thermal management, and proper operation of the IC. A typical PCB layout example is shown as follow. The following rules should be followed carefully during the design of the PCB layout:

- 1) Place IC filter and programming components directly next to the IC. These components include (CVCC, RCS). Reference all these components to the GND pin.

- 2) Do not run power GND currents through signal GND!

- 3) For best thermal management, place thermal vias in the source pad area to conduct the heat out through the bottom of the package and through the PCB board to other layers.

- 4) Use large PCB thermal planes (connected with thermal vias to the source pad) and additional PCB layers to reduce IC temperatures as much as possible.

Final Datasheet 18 Rev Dec 05, 2024

**Step 1**. Place GaN IC and components on PCB. Place components as close as possible to IC!

**Step 2**. Route all connections on single layer.

Make large copper areas on and around Source pad!

**Step 3**. Place many thermal vias inside source pad and inside source copper areas.

(dia=0.65mm, hole=0.33mm, pitch=0.925mm, via wall 1mil)

**Step 4**. Place large copper areas on other layers. Make all thermal copper areas as large as possible!

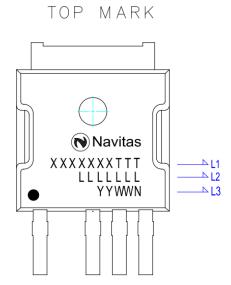

## 11. Package outline

| Marking<br>Line | Marking<br>Symbol | Content<br>Description                                                                                       |

|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------|

| L1              | xxxxxx            | Part Number : First 7 characters of the Navitas Part Number<br>Example : NV6143CP01, XXXXXXX = NV6143C       |

|                 | ттт               | Optional Trim Code : 8th, 9th, and 10th digit of the Navitas Part<br>Number. Example : NV6143CP01, TTT = P01 |

| L2              | LLLLLLL           | Lot Number: Max 7 digits assembly lot number for marking<br>Example: NC31900                                 |

| L3              | YY                | Year Code: Last 2 digits of the year<br>Example: 2023, YY=23                                                 |

|                 | ww                | Week Code: 01 - 53                                                                                           |

|                 | N                 | Supplier Site Code : Y = HYME                                                                                |

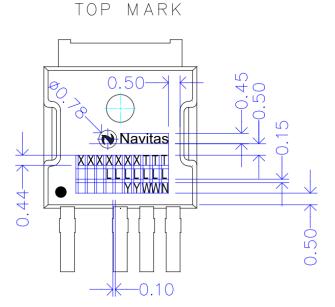

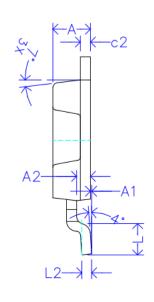

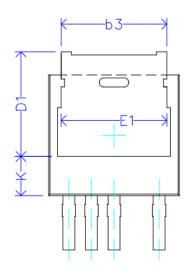

## 11. Package outline (cont.)

TOP VIEW

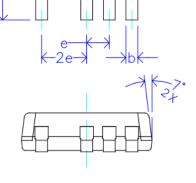

| SYMBOL | MIN   | NOM   | MAX   |

|--------|-------|-------|-------|

| Α      | 1.80  | 1.90  | 2.00  |

| A1     | 0.00  | -     | 0.20  |

| A2     | 0.60  | 0.70  | 0.80  |

| b      | 0.508 | 0.60  | 0.711 |

| b3     | 5.21  | -     | 5.46  |

| c2     | 0.41  | 0.508 | 0.61  |

| D      | 6.00  | 6.10  | 6.22  |

| D1     | 4.90  | -     | -     |

| E      | 6.40  | 6.60  | 6.73  |

|        |       |       |       |

| SYMBOL                            | MIN       | NOM         | MAX  |  |

|-----------------------------------|-----------|-------------|------|--|

| E1                                | 5.10      | 5.30        | 5.50 |  |

| е                                 |           | 1.14 BSC    |      |  |

| L                                 | 1.34      | 1.585       | 1.77 |  |

| L1                                | 2.743 REF |             |      |  |

| L2                                | 0.41      | 0.508       | 0.61 |  |

| L3                                | 0.88      | -           | 1.28 |  |

| K                                 | 1.98      | -           | -    |  |

| Package Draft Angles 5-9 degrees  |           |             |      |  |

| Foot Angle                        |           | 0-8 degrees |      |  |

| Gauge Plane for L                 |           | 0.508       |      |  |

| Notes :                           |           |             |      |  |

| All dimentions in mm.             |           |             |      |  |

| 2. Reference JEDEC TO-252F VAR AD |           |             |      |  |

| 3. 100% Sn Plating                |           |             |      |  |

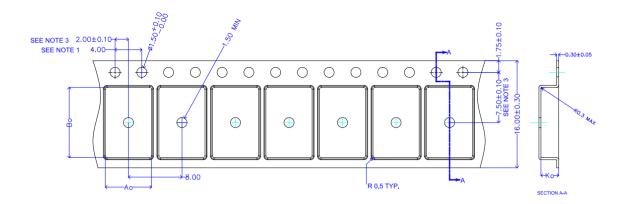

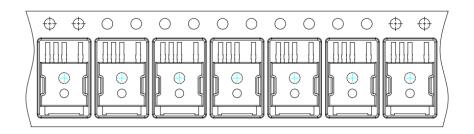

## 12. Tape and Reel Dimensions

| Notes                                                                                               |       |  |  |

|-----------------------------------------------------------------------------------------------------|-------|--|--|

| Ao                                                                                                  | 6.9   |  |  |

| Во                                                                                                  | 10.50 |  |  |

| Ko                                                                                                  | 2.65  |  |  |

| 1. 10 sproket hole pitch cumulative tolerance ±0.2                                                  |       |  |  |

| 2. Camber in compliance with EIA 481                                                                |       |  |  |

| Pocket position relative to sprocket hole measured     as true position of pocket, not pocket hole. |       |  |  |

Final Datasheet 22 Rev Dec 05, 2024

## 13. Ordering Information

| Part Number | Operating<br>Temperature Grade   | Storage<br>Temperature Range        | Note                  | Package | MSL<br>Rating | Packing<br>(Tape & Reel) |

|-------------|----------------------------------|-------------------------------------|-----------------------|---------|---------------|--------------------------|

| NV6146CQ01  | -55 °C to +150 °C T <sub>J</sub> | -55 °C to +150 °C T <sub>STOR</sub> | Isolated topology     | DPAK-4L | 3             | 2,000: 13" Reel          |

| NV6146CP01  | -55 °C to +150 °C T <sub>J</sub> | -55 °C to +150 °C T <sub>STOR</sub> | Non-isolated topology | DPAK-4L | 3             | 2,000: 13" Reel          |

Final Datasheet 23 Rev Dec 05, 2024

### 14. Revision History

| Date       | Status    | Notes                                                                          |  |

|------------|-----------|--------------------------------------------------------------------------------|--|

| 07-25-2024 | Datasheet | First publication                                                              |  |

| 04-09-2024 | Datasheet | Update TnR information and VCC range change                                    |  |

| 12-05-2024 | Datasheet | Update Order Information and correct Ron and V <sub>SD</sub> testing condition |  |

|            |           |                                                                                |  |

|            |           |                                                                                |  |

|            |           |                                                                                |  |

## 15. 20-Year Limited Product Warranty

The 20-year limited warranty applies to all packaged Navitas GaNFast Power ICs in mass production, subject to the terms and conditions of, Navitas' express limited product warranty, available at <a href="https://navitassemi.com/terms-conditions">https://navitassemi.com/terms-conditions</a>. The warranted specifications include only the MIN and MAX values only listed in Absolute Maximum Ratings, ESD Ratings and Electrical Characteristics sections of this datasheet. Typical (TYP) values or other specifications are not warranted.

#### **Additional Information**

DISCLAIMER Navitas Semiconductor Inc. (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties.

Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems.

Products supplied under Navitas Terms and Conditions.

Navitas Semiconductor, Navitas, iDrive, AllGaN and associated logos are registered trademarks of Navitas.

Copyright ©2020 Navitas Semiconductor Inc. All rights reserved

Navitas Semiconductor Inc., 2101 E El Segundo Blvd, Suite 205, El Segundo, California 90245, USA.

Contact info@navitassemi.com

#### **IMPORTANT NOTICES AND DISCLAIMERS**

EXCEPT TO THE EXTENT THAT INFORMATION IN THIS DATA SHEET IS EXPRESSLY AND SPECIFICALLY WARRANTED IN WRITING BY NAVITAS SEMICONDUCTOR ("NAVITAS"), EITHER PURSUANT TO THE TERMS AND CONDITIONS OF THE LIMITED WARRANTY CONTAINED IN NAVITAS' STANDARD TERMS AND CONDITIONS OF SALE OR A WRITTEN AGREEMENT SIGNED BY AN AUTHORIZED NAVITAS REPRESENTATIVE, (1) ALL INFORMATION IN THIS DATA SHEET OR OTHER RELIABILITY AND TECHNICAL DATA, AND ANY OTHER DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE OR TOOLS, SAFETY INFORMATION AND OTHER RESOURCES, ARE PROVIDED "AS IS" AND WITH ALL FAULTS; AND (2) NAVITAS MAKES NO WARRANTIES OR REPRESENTATIONS AS TO ANY SUCH INFORMATION OR RESOURCES, IN THIS DATA SHEET OR OTHERWISE, AND HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

**CUSTOMER RESPONSIBILITIES.** This data sheet and other design resources and information provided by Navitas are intended only for technically trained and skilled developers designing with Navitas- or GeneSiC-branded products ("**Products**"). Performance specifications and the operating parameters of Products described herein are determined in the independent state and may not perform the same way when installed in customer products. The customer (or other user of this data sheet) is solely responsible for (a) designing, validating and testing the products and systems in which Products are incorporated; (b) designing, validating and testing the application in which Products are incorporated; (c) ensuring the application meets applicable standards and any safety, security, regulatory or other requirements; (d) evaluating the suitability of Products for the intended application and the completeness of the information in this data sheet with respect to such application; (e) procuring and/or developing production firmware, if applicable; and (f) completing system qualification, compliance and safety testing, EMC testing, and any automotive, high-reliability or other system qualifications that apply.

**NON-AUTHORIZED USES OF PRODUCTS.** Except to the extent expressly provided in a writing signed by an authorized Navitas representative, Products are not designed, authorized or warranted for use in extreme or hazardous conditions; aircraft navigation, communication or control systems; aircraft power and propulsion systems; air traffic control systems; military, weapons, space-based or nuclear applications; life-support devices or systems, including but not limited to devices implanted into the human body and emergency medical equipment; or applications where product failure could lead to death, personal injury or severe property or environmental damage. The customer or other persons using Products in such applications without Navitas' agreement or acknowledgement, as set forth in a writing signed by an authorized Navitas representative, do so entirely at their own risk and agree to fully indemnify Navitas for any damages resulting from such improper use. In order to minimize risks associated with such applications, you should provide adequate design and operating safeguards.

CHANGES TO, AND USE OF, THIS DATA SHEET. This data sheet and accompanying information and resources are subject to change without notice. Navitas grants you permission to use this data sheet and accompanying resources only for the development of an application that uses the Products described herein and subject to the notices and disclaimers set forth above. Any other use, reproduction or display of this data sheet or accompanying resources and information is prohibited. No license is granted to any Navitas intellectual property right or to any third-party intellectual property right. Navitas disclaims any responsibility for, and you will fully indemnify Navitas and its representatives against, any claims, damages, costs, losses and liabilities arising out of your use of this data sheet and any accompanying resources and information.

**TERMS AND CONDITIONS.** All purchases and sales of Products are subject to <u>Navitas' Standard Terms and Conditions of Sale</u>, including the limited warranty contained therein, unless other terms and conditions have been agreed in a writing signed by an authorized Navitas representative. This data sheet, and Navitas' provision of this data sheet or other information and resources, do not expand or otherwise alter those terms and conditions.

Navitas, GeneSiC, the Navitas and GeneSiC logos, GaNFast, GaNSafe and other Navitas marks used herein are trademarks or registered trademarks of Navitas Semiconductor Limited or its affiliates. Other trademarks used herein are the property of their respective owners.

| Contact:                               |                                                                           |                                      |

|----------------------------------------|---------------------------------------------------------------------------|--------------------------------------|

| ////////////////////////////////////// | ////<br>g <b>Foote</b> r on <b>at least the first page</b> of the data si | heet (do not include on last nage)]  |

| ////////////////////////////////////// |                                                                           | ricet (do not include on tast page)] |

Copyright © 2024 Navitas Semiconductor Limited and affiliates. All rights reserved.

SEE IMPORTANT NOTICES AND DISCLAIMERS AT THE END OF THIS DATA SHEET REGARDING THE INFORMATION IN THIS DATA SHEET, THE USE OF OUR PRODUCTS, AND YOUR RESPONSIBILITIES RELATING TO SUCH USE.

Final Datasheet 25 Rev Dec 05, 2024