# BOS1921/BOS1931 Piezo Haptic Driver with Digital Front End

## 1 Features

- High-Voltage Low Power Piezo Driver

- Drives 100 nF at 190 V<sub>pk-pk</sub> and 300 Hz while consuming only 350 mW

- Drives Capacitive Loads up to 820 nF

- Energy Recovery

- Differential Output

- Small Solution Footprint, QFN & WLCSP

- Advanced Piezo Sensing Capabilities (BOS1921 only)

- o 7.6 mV Sensing Resolution

- Interrupt Generation

- o Automatic Triggering of Haptic Feedback

- Integrated Digital Front End with I3C/I<sup>2</sup>C

- o 1024 sample Internal FIFO Interface

- 1.8 V to 5.0 V Digital I/O Supply

- Waveform Synthesizer (WFS)

- Supports Continuous Waveforms Playback

- State Retention in SLEEP Mode

- Fast Start Up Time of Less Than 300 μs

- Multi-Actuator Synchronization

- Wide Supply Voltage Range of 3 V to 5.5 V

## 2 Applications

- Mobile Phones and Tablets

- Portable Computers, Keyboards and Mice

- Gaming Controllers, Wearables

- Electronic Cooling

- Micropump

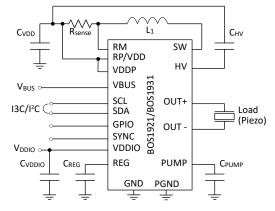

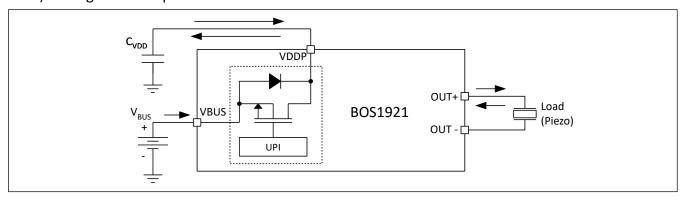

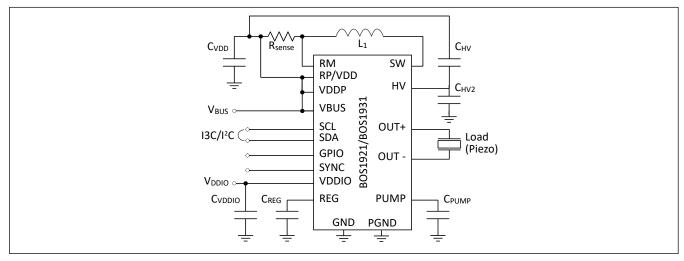

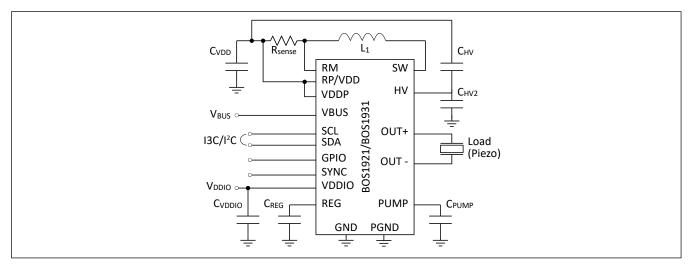

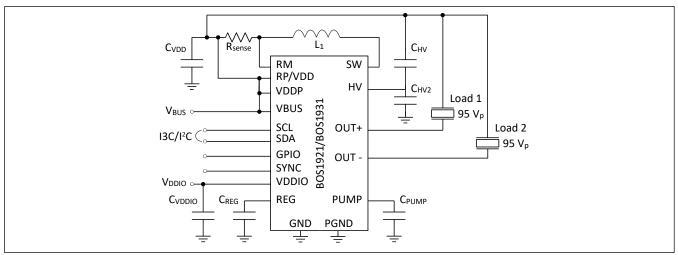

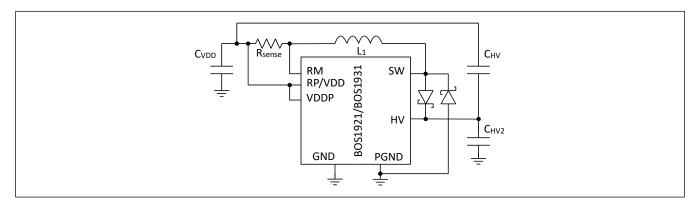

Figure 1: Simplified schematic

## 3 Description

The BOS1921 (driving + sensing) and BOS1931 (driving) are a single-chip piezo actuator driver with energy recovery, based on Boreas' patented CapDrive™ technology. It can drive actuators with waveforms up to 190 V<sub>pk-pk</sub> while operating from a 3 to 5.5 V supply voltage. Its low power and small size make it ideal for a variety of applications requiring minimal power consumption.

The BOS1921 features high-resolution piezo sensing capabilities, allowing haptic feedback to be automatically played when detection conditions are met.

The BOS1921/BOS1931 differential driver achieves low distortion waveforms and quiet actuator operation. All settings are adjustable through the digital front end to reduce the BOM.

Data and configuration parameters are easily communicated to the BOS1921/BOS1931 through its two-wire MIPI I3C interface. The MIPI I3C is also backward compatible with I<sup>2</sup>C for easy integration in most systems. A flexible deep FIFO enables the streaming of digital waveform data for playback or the transmission of burst data for more bandwidth efficiency. The BOS1921/BOS1931 also integrates a waveform synthesizer and 2 kB of RAM waveform memory to generate HD haptic waveforms with minimal communication bandwidth.

A dedicated SYNC pin can synchronize multiple BOS1921/BOS1931 controllers to simultaneously drive multiple actuators within 2  $\mu$ s.

With a typical start-up time of less than 300  $\mu$ s, the device latency is negligible in most systems.

Various safety systems protect the BOS1921/BOS1931 from damage in case of a fault.

See section 9 for package dimensions and section 11 for ordering information.

## **TABLE OF CONTENT**

| 1 FEATURES                                            | 1  |

|-------------------------------------------------------|----|

| 2 APPLICATIONS                                        | 1  |

| 3 DESCRIPTION                                         | 1  |

| 4 PINS & BUMPS CONFIGURATION AND FUNCTIONS            | 3  |

| 5 SPECIFICATIONS                                      | 5  |

| 5.1 Absolute Maximum Ratings                          | 5  |

| 5.2 THERMAL RESISTANCE                                |    |

| 5.3 RECOMMENDED OPERATING CONDITIONS                  | 5  |

| 5.4 ELECTRICAL CHARACTERISTICS                        |    |

| 5.5 TIMING CHARACTERISTICS                            |    |

| 5.6 TYPICAL PERFORMANCE CHARACTERISTICS               |    |

| 6 FUNCTIONAL DESCRIPTION                              | 11 |

| 6.1 Overview                                          |    |

| 6.2 FEATURES                                          |    |

| 6.3 DIGITAL INTERFACE                                 |    |

| 6.4 PIEZO ACTUATOR SENSING (BOS1921 ONLY)             |    |

| 6.5 DIRECT MODE                                       | _  |

| 6.6 FIFO MODE                                         |    |

| 6.7 RAM PLAYBACK MODE                                 |    |

| 6.8 RAM SYNTHESIS MODE                                |    |

| 6.9 WFS COMMAND INTERPRETER                           |    |

| 6.10 REGISTER MAP                                     |    |

| 7 IMPLEMENTATION                                      |    |

| 7.1 DIFFERENTIAL OUTPUT CONFIGURATION                 |    |

| 7.2 SINGLE-ENDED CONFIGURATION                        |    |

| 7.3 External Components                               |    |

| 7.4 Initialization                                    |    |

| 7.5 DESIGN METHODOLOGY: SELECTION OF COMPONENT        |    |

| 7.6 DESIGN METHODOLOGY: PROGRAMMING                   |    |

| 7.7 Noise Reduction                                   | 87 |

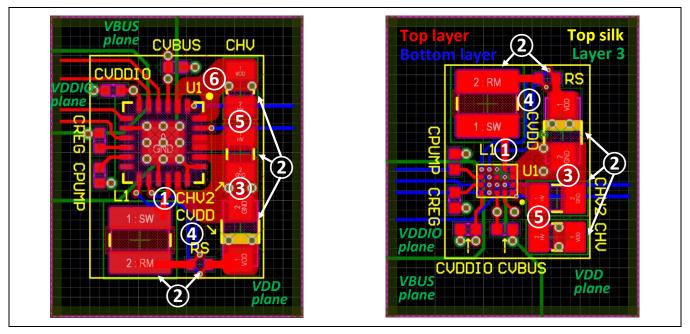

| 8 PCB LAYOUT EXAMPLE                                  | 88 |

| 9 MECHANICAL                                          | 90 |

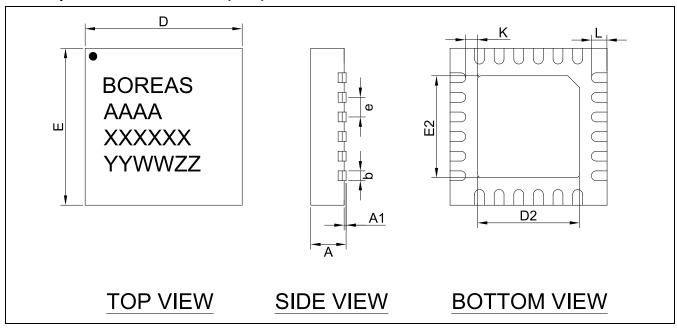

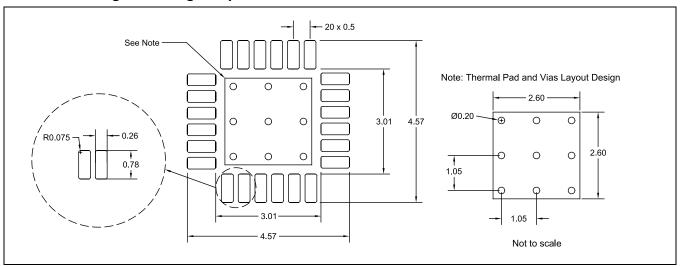

| 9.1 QFN PACKAGE DESCRIPTION                           | 90 |

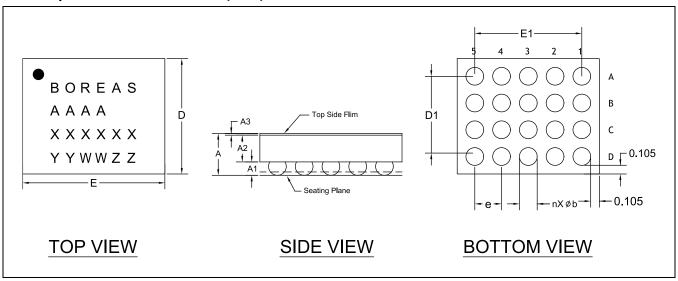

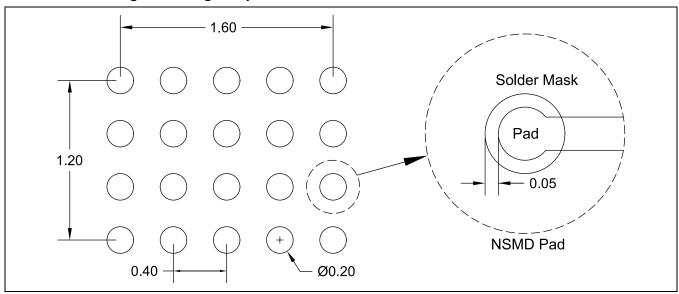

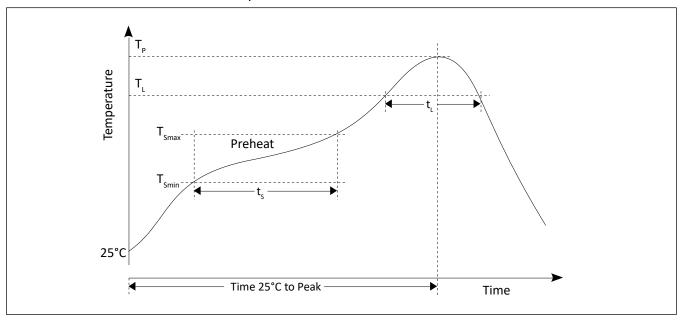

| 9.2 WLCSP PACKAGE DESCRIPTION                         | 92 |

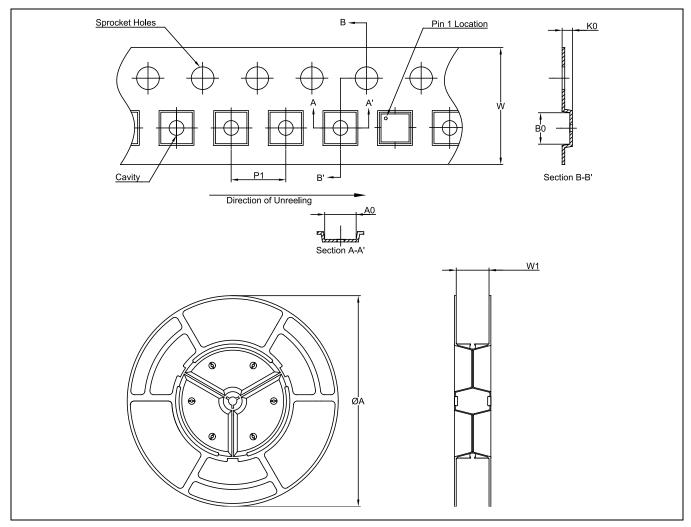

| 9.3 TAPE AND REEL SPECIFICATIONS                      | 95 |

| 10 KNOWN ISSUES                                       | 96 |

| 10.1 Incorrect Activation of Output Bridge Protection |    |

| 10.2 TIMEOUT RESETS PLAY_SRATE                        | 96 |

| 10.3 WAVEFORM AMPLITUDE DRIFT WITH RELOFF OPTION      |    |

| 10.4 MINIMUM SLEW-RATE OF VBUS SUPPLY                 | 96 |

| 11 ORDERING INFORMATION                               | 97 |

| 12 DOCUMENT HISTORY                                   | 98 |

| 13 NOTICE AND WARNING                                 | 99 |

# **4 Pins & Bumps Configuration and Functions**

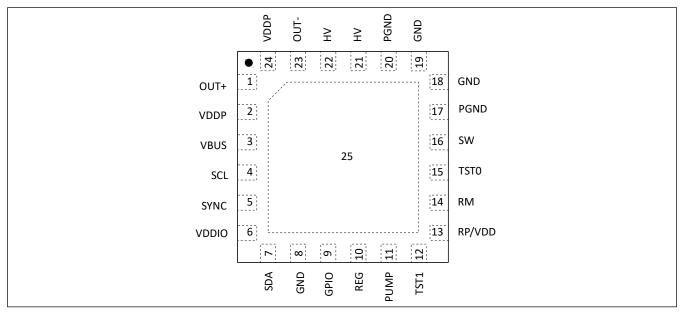

Figure 2: QFN 24L 4.0mm × 4.0mm package with exposed thermal pad (TOP VIEW; NOT TO SCALE)

Table 1: QFN package pins description

| PIN NO. | NAME   | TYPE         | DESCRIPTION                                            |  |

|---------|--------|--------------|--------------------------------------------------------|--|

| 1       | OUT+   | Output       | Positive Differential Output                           |  |

| 2       | VDDP   | Power        | Intermediate Supply Voltage                            |  |

| 3       | VBUS   | Power        | Main Power Supply                                      |  |

| 4       | SCL    | Input        | I3C/I <sup>2</sup> C clock                             |  |

| 5       | SYNC   | Input/Output | Synchronization pin, tie de ground if unused           |  |

| 6       | VDDIO  | Power        | Digital IO Power Supply                                |  |

| 7       | SDA    | Input/Output | I3C/I <sup>2</sup> C data                              |  |

| 8       | GND    | Power        | Supply Ground                                          |  |

| 9       | GPIO   | Input/Output | General-purpose input output                           |  |

| 10      | REG    | Power        | Internal 1.8 V Regulator Output                        |  |

| 11      | PUMP   | Power        | Internal 5 V Charge Pump Voltage                       |  |

| 12      | TST1   | -            | No connect                                             |  |

| 13      | RP/VDD | Power        | Current Sense Positive Input / Supply Voltage          |  |

| 14      | RM     | Input        | Current Sense Negative Input                           |  |

| 15      | TST0   | -            | Connect to GND                                         |  |

| 16      | SW     | Power        | Internal Power Converter Switch Pin                    |  |

| 17      | PGND   | Power        | Supply Ground of the Power Stage                       |  |

| 18      | GND    | Power        | Supply Ground                                          |  |

| 19      | GND    | Power        | Supply Ground                                          |  |

| 20      | PGND   | Power        | Supply Ground of the Power Stage                       |  |

| 21      | HV     | Power        | High-Voltage Output                                    |  |

| 22      | HV     | Power        | High-Voltage Output                                    |  |

| 23      | OUT-   | Output       | Negative Differential Output                           |  |

| 24      | VDDP   | Power        | Intermediate Supply Voltage                            |  |

| 25      | GND    | Power        | Exposed thermal pad is GND and must be soldered to PCB |  |

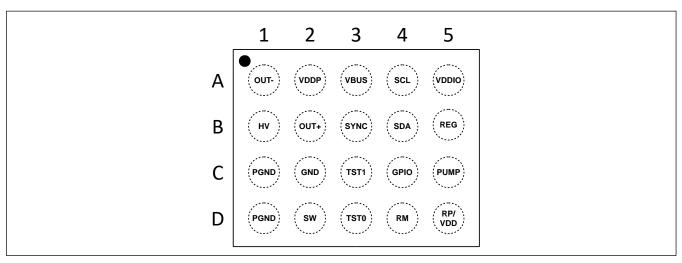

Figure 3: WLCSP 20B 2.1mm × 1.7mm package (TOP VIEW; NOT TO SCALE)

Table 2: WLCSP package bumps description

| BUMP NO. | NAME   | TYPE         | DESCRIPTION                                   |

|----------|--------|--------------|-----------------------------------------------|

| A1       | OUT-   | Output       | Negative Differential Output                  |

| A2       | VDDP   | Power        | Intermediate Supply Voltage                   |

| A3       | VBUS   | Power        | Main Power Supply                             |

| A4       | SCL    | Input        | I3C/I <sup>2</sup> C clock                    |

| A5       | VDDIO  | Power        | Digital IO Power Supply                       |

| B1       | HV     | Power        | High-Voltage Output                           |

| B2       | OUT+   | Output       | Positive Differential Output                  |

| В3       | SYNC   | Input/Output | Synchronization pin                           |

| B4       | SDA    | Input/Output | I3C/I <sup>2</sup> C data                     |

| B5       | REG    | Power        | Internal 1.8 V Regulator Output               |

| C1       | PGND   | Power        | Supply Ground of the Power Stage              |

| C2       | GND    | Power        | Supply Ground                                 |

| C3       | TST1   | -            | No connect                                    |

| C4       | GPIO   | Input/Output | General-purpose input output                  |

| C5       | PUMP   | Power        | Internal 5 V Charge Pump Voltage              |

| D1       | PGND   | Power        | Supply Ground of the Power Stage              |

| D2       | SW     | Power        | Internal Power Converter Switch Pin           |

| D3       | TST0   | -            | Connect to GND                                |

| D4       | RM     | Input        | Current Sense Negative Input                  |

| D5       | RP/VDD | Input        | Current Sense Positive Input / Supply Voltage |

## **5 Specifications**

## **5.1 Absolute Maximum Ratings**

Table 3: Absolute maximum ratings<sup>‡</sup>

|   | SYMBOL           | PARAMETER                          | MIN            | NOM | MAX | UNIT |

|---|------------------|------------------------------------|----------------|-----|-----|------|

| 1 |                  | Voltage at pins HV, OUT+, OUT-, SW | -0.3           |     | 110 | V    |

| 2 |                  | Voltage at all other pins          | -0.3           |     | 7   | V    |

| 3 | T <sub>stg</sub> | Storage temperature                | -65            |     | 150 | °C   |

| 4 | Tı               | Junction Temperature               | -40            |     | 150 | °C   |

| 5 | SOA              | Safe operating area                | See Figure 14. |     | -   |      |

<sup>‡</sup>Exceeding these values may cause permanent damage. Functional operation under these conditions is not guaranteed.

### 5.2 Thermal Resistance

Table 4: Thermal resistance<sup>‡</sup>

|   | SYMBOL | PARAMETER                    | PACKAGE                 | MIN | NOM (1,2) | MAX | UNIT |

|---|--------|------------------------------|-------------------------|-----|-----------|-----|------|

| 1 | ӨЈА    | Thermal resistance: junction | QFN 24L 4.0mm × 4.0mm   |     | TBD       |     | °C/W |

|   |        | to ambient                   | WLCSP 20B 2.1mm × 1.7mm |     | 100       |     | °C/W |

<sup>‡</sup>Power dissipated in the package is not obvious to calculate. Please consult Boréas Technologies before using these parameters.

## **5.3 Recommended Operating Conditions**

Table 5: Recommended operating conditions

|   | SYMBOL                                                | PARAMETER                   | TEST CONDITIONS                                                          | MIN  | NOM | MAX  | UNIT |

|---|-------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------|------|-----|------|------|

| 1 | T <sub>A</sub>                                        | Operating Temperature       | Operating free-air temperature                                           | -40  |     | 85   | °C   |

| 2 | <i>V<sub>BUS</sub>, V<sub>DD</sub></i> <sup>(1)</sup> | Supply voltage              |                                                                          | 3.0  |     | 5.5  | V    |

| 3 | $V_{DDIO}^{(2)}$                                      | I/O Supply voltage          |                                                                          | 1.62 |     | 5.5  | V    |

| 4 | CL                                                    | Load capacitance            | V <sub>OUT</sub> = 190 V <sub>pk-pk</sub> ,<br>f <sub>OUT</sub> = 300 Hz |      |     | 100  | nF   |

|   |                                                       |                             | V <sub>OUT</sub> = 100 V <sub>pk-pk</sub> ,<br>f <sub>OUT</sub> = 220 Hz |      |     | 470  | nF   |

|   |                                                       |                             | V <sub>OUT</sub> = 100 V <sub>pk-pk</sub> ,<br>f <sub>OUT</sub> = 130 Hz |      |     | 820  | nF   |

| 5 | L <sub>1</sub>                                        | Inductance                  |                                                                          | 10   |     | 68   | μН   |

| 6 | Rsense                                                | Sense resistor              |                                                                          | 0.2  |     | 1.0  | Ω    |

| 7 | fоuт                                                  | Output frequency            | <u>PLAY MODE[1:0]</u> = 0x3                                              | 3.9  |     | 1000 | Hz   |

| 8 | Isw                                                   | Transient current at SW pin |                                                                          |      |     | 1.3  | Α    |

<sup>(1)</sup> If the Unidirectional Power Input mode is enabled ( $\underline{UPI}$  bit set to 0x1),  $V_{DD}$  may increase above the maximum recommended operating condition, see section 6.2.13.

<sup>(2)</sup> Digital I/O voltage (V<sub>DDIO</sub>) must match the communication interface voltage.

## **5.4 Electrical Characteristics**

Table 6: Electrical characteristics. Conditions:  $T_A = 25$ °C,  $V_{BUS} = 3.6$  V (unless otherwise noted)

|    | SYMBOL                 | PARAMETER                                           | TEST CONDITIONS                                                                                          | MIN                    | NOM       | MAX                    | UNIT               |

|----|------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------|-----------|------------------------|--------------------|

| 1  | $V_{REG}$              | Voltage at REG pin                                  |                                                                                                          | 1.75                   | 1.80      | 1.85                   | ٧                  |

| 2  | VIL                    | Digital low-level input voltage                     | SDA, SCL, GPIO & SYNC pins                                                                               |                        |           | 0.5                    | ٧                  |

| 3  | V <sub>IH</sub>        | Digital high-level input voltage                    |                                                                                                          | V <sub>DDIO</sub> ×0.7 |           | V <sub>DDIO</sub> +0.3 | V                  |

| 4  | VoL                    | Digital low-level output voltage                    |                                                                                                          |                        |           | 0.4                    | V                  |

| 5  | V <sub>OH</sub>        | Digital high-level output voltage                   |                                                                                                          | V <sub>DDIO</sub> ×0.8 |           |                        |                    |

| 6  | V <sub>OUT(FS)</sub>   | Full-scale output voltage                           |                                                                                                          | 186                    | 190       | 194                    | V <sub>pk-pk</sub> |

| 7  | I <sub>Q_VBUS</sub>    | V <sub>BUS</sub> Quiescent current                  | SLEEP State <sup>(1)(2)</sup> <u>OE</u> =0x0, <u>DS</u> =0x1, <u>RET</u> =0x1                            |                        | 0.6       | 10                     | μΑ                 |

|    |                        |                                                     | SLEEP State  OE=0x0, DS=0x1, RET=0x0                                                                     |                        | 2.4       |                        | μΑ                 |

|    |                        |                                                     | IDLE State OE=0x0, DS=0x0                                                                                |                        | 530       |                        | μΑ                 |

| 8  | I <sub>BUS,AVG</sub>   | Average V <sub>BUS</sub> supply current             | SENSING=0x1 <sup>(3)</sup>                                                                               |                        | 1.9       |                        | mA                 |

|    |                        | during operation & OE=0x1                           | F <sub>OUT</sub> = DC<br>V <sub>OUT</sub> = 95 V<br>C <sub>Load</sub> = 100 nF                           |                        | 3.7       |                        | mA                 |

|    |                        |                                                     | $f_{OUT} = 300 \text{ Hz}$ $V_{OUT} = 190 \text{ V}_{pk-pk}$ $C_{Load} = 100 \text{ nF}$                 |                        | 90        |                        | mA                 |

|    |                        |                                                     | f <sub>OUT</sub> = 200 Hz<br>V <sub>OUT</sub> = 190 Vpk-pk<br>C <sub>L</sub> = 10 nF<br><u>CCM</u> = 0x0 |                        | 14.5      |                        | mA                 |

| 9  | THD+N                  | Total Harmonic Distortion +<br>Noise <sup>(2)</sup> | $ f_{OUT} = 300 \text{ Hz} $ $V_{OUT} = 190 \text{ V}_{pk-pk} $ $C_{Load} = 100 \text{ nF} $             |                        | 0.3       | 1                      | %                  |

| 10 | f <sub>s-FIFO</sub>    | Programmable FIFO playback rate                     | PLAY_SRATE[2:0]=0x0<br>PLAY_SRATE[2:0]=0x7                                                               | 1008<br>7.875          | 1024<br>8 | 1040<br>8.125          | ksps               |

| 11 | PSR <sup>(3)</sup>     | Piezo Sensing Resolution                            | CONFIG.GAINS=0x1                                                                                         |                        | 7.6       |                        | mV                 |

| 12 | t <sub>start</sub> (2) | Start-up Time                                       | Time from SLEEP mode to haptic waveform playback                                                         |                        |           | 300                    | μs                 |

| 13 | DHL <sup>(2)(3)</sup>  | Sensing Detection to Haptic<br>Feedback Latency     | Time from sensing detection event to automatic playback                                                  |                        |           | 30                     | μs                 |

<sup>(1)</sup> The VDDIO supply should be powered off when state retention is disabled ( $\underbrace{RET}$  bit set to 0x1) to minimize the total quiescent current of the device.

<sup>(2)</sup> Validated by design.

<sup>(3)</sup> BOS1921 only.

## **5.5 Timing Characteristics**

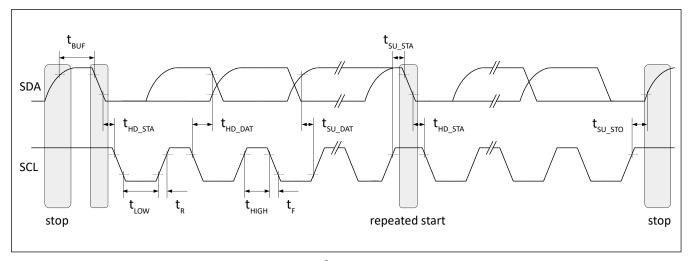

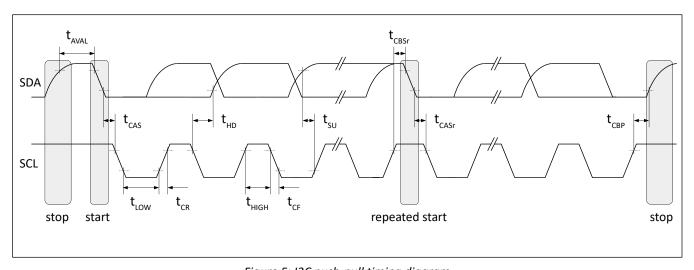

## 5.5.1 I<sup>2</sup>C

Table 7: Timing characteristics. Condition:  $I^2C$  communication mode,  $T_A = 25$ °C,  $V_{DDIO} = 1.8$  V, SDA/SCL load = 50 pF

|    |                     |                                                                | FAST<br>MODE |     | FAST<br>MODE + |     |      |

|----|---------------------|----------------------------------------------------------------|--------------|-----|----------------|-----|------|

|    | SYMBOL              | PARAMETER                                                      | MIN          | MAX | MIN            | MAX | UNIT |

| 1  | f <sub>SCL</sub>    | SCL clock frequency <sup>(1)</sup>                             | 0            | 0.4 | 0              | 1.0 | MHz  |

| 2  | t <sub>LOW</sub>    | SCL low period                                                 | 1300         |     | 500            |     | ns   |

| 3  | t <sub>HIGH</sub>   | SCL high period                                                | 600          |     | 260            |     | ns   |

| 4  | t <sub>R</sub>      | SDA/SCL rise time <sup>(1)</sup>                               | 20           | 300 | -              | 120 | ns   |

| 5  | t <sub>F</sub>      | SDA/SCL fall time <sup>(1)</sup>                               | -            | 300 | -              | 120 | ns   |

| 6  | t <sub>SU_DAT</sub> | Data setup time <sup>(1)</sup>                                 | 100          |     | 50             |     | ns   |

| 7  | thd_dat             | Data hold time <sup>(1)</sup>                                  | 0            | -   | 0              | -   | ns   |

| 8  | tsu_sta             | Setup time for a repeated START condition <sup>(1)</sup>       | 600          |     | 260            |     | ns   |

| 9  | t <sub>HD_STA</sub> | Hold time for a (repeated) START condition <sup>(1)</sup>      | 600          |     | 260            |     | ns   |

| 10 | t <sub>SU_STO</sub> | Setup time for STOP condition <sup>(1)</sup>                   | 600          |     | 260            |     | ns   |

| 11 | <b>t</b> BUF        | Bus free time (time between the STOP and START conditions) (1) | 1300         |     | 500            |     | ns   |

| 12 | t <sub>SPIKE</sub>  | Spike suppression pulse width <sup>(1)</sup>                   | 0            | 50  | 0              | 50  | ns   |

## (1) Validated by design.

Figure 4: I<sup>2</sup>C timing diagram

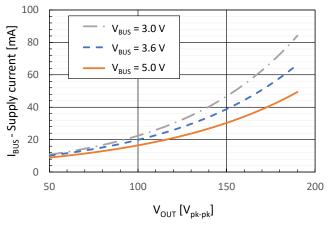

#### 5.5.2 I3C

Table 8: Timing characteristics. Condition: I3C push-pull, T<sub>A</sub> = 25°C, V<sub>DDIO</sub> = 1.8 V, SDA/SCL load = 50 pF

|    | SYMBOL                       | PARAMETER                                 | MIN            | MAX                                                        | UNIT |

|----|------------------------------|-------------------------------------------|----------------|------------------------------------------------------------|------|

| 1  | f <sub>SCL</sub>             | SCL clock frequency (1)                   | 0.01           | 12.5                                                       | MHz  |

| 2  | t <sub>LOW</sub>             | SCL low period                            | 24             |                                                            | ns   |

| 3  | t <sub>нібн</sub>            | SCL high period                           | 24             | 41 (2)                                                     | ns   |

| 4  | t <sub>CR</sub>              | SCL rise time <sup>(1)</sup>              |                | The minimum between whether 150×106/f <sub>SCL</sub> or 60 | ns   |

| 7  | <b>t</b> CF                  | SCL fall time (1)                         |                | The minimum between whether 150×106/f <sub>scl</sub> or 60 | ns   |

| 8  | tsu                          | Data setup time                           | 3              |                                                            | ns   |

| 9  | t <sub>HD</sub> (controller) | Data hold time                            | tCR +3, tCF +3 |                                                            | ns   |

| 10 | t <sub>HD (target)</sub>     | Data hold time                            | 0              |                                                            | ns   |

| 11 | t <sub>CBSr</sub>            | Clock before repeated START condition (1) | 19.2           |                                                            | ns   |

| 12 | tcas                         | Clock after START condition (1)           | 38.4           |                                                            | ns   |

| 13 | tcasr                        | Clock after repeated START condition (1)  | 38.4           |                                                            | ns   |

| 14 | t <sub>CBP</sub>             | Clock before STOP condition (1)           | 19.2           |                                                            | ns   |

| 15 | t <sub>AVAL</sub>            | Bus available <sup>(1)</sup>              | 1              |                                                            | μs   |

<sup>(1)</sup> Validated by design.

<sup>(2)</sup> This maximum high period may be exceeded when the signals can be safely seen by legacy  $I^2C$  devices.

Figure 5: I3C push-pull timing diagram

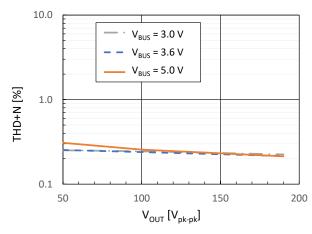

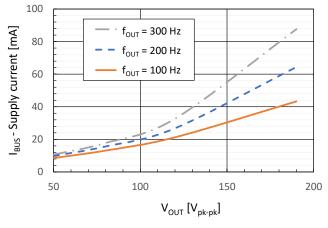

## **5.6 Typical Performance Characteristics**

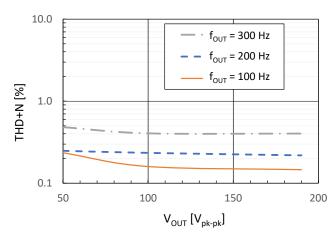

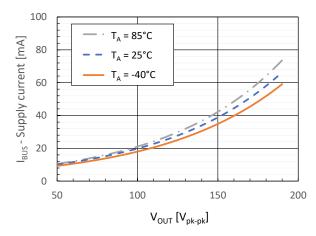

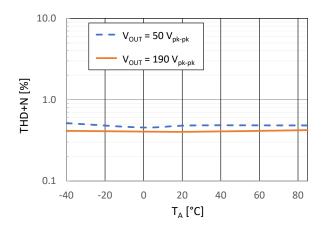

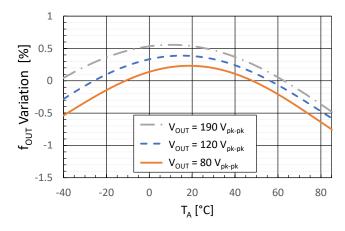

Typical performance characteristics for the following conditions:  $T_A = 25$ °C,  $V_{BUS} = 3.6$  V,  $C_L = 100$  nF,  $V_{OUT} = 190$   $V_{pk-pk}$  and  $f_{OUT} = 200$  Hz (unless otherwise noted).

Figure 6: Supply Current vs Output Voltage

Figure 7: Total Harmonic Distortion + Noise vs Output Voltage

Figure 8: Supply Current vs Output Voltage

Figure 9: Total Harmonic Distortion + Noise vs Output Voltage

Figure 10: Supply Current vs Operating free-air Temperature

Figure 11: Total Harmonic Distortion + Noise vs Operating free-air Temperature

600 V<sub>BUS</sub> = 5.0 V V<sub>BUS</sub> = 3.6 V V<sub>BUS</sub> = 3.6 V -40 -20 0 20 40 60 80 T<sub>A</sub> [°C]

Figure 12: Output Frequency Variation vs Operating free-air Temperature

Figure 13: Supply Quiescent Current in IDLE Mode vs Operating free-air Temperature

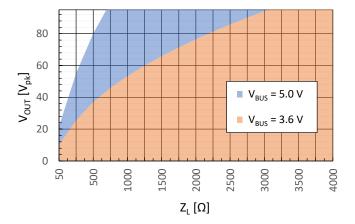

Figure 14: Safe Operating Area at Isw max

## **6 Functional Description**

### 6.1 Overview

The BOS1921/BOS1931 is a highly integrated low-power piezo actuator driver with an integrated digital front end and energy recovery, based on Boreas's patented CapDrive<sup>TM</sup> technology. The device requires a single low-voltage supply and 7 passive components to generate waveforms of up to 190  $V_{pk-pk}$ .

The digital interface enables the transmission of the digital waveform data from any MCU with an I3C or  $I^2C$  interface to the BOS1921/BOS1931. A flexible FIFO interface enables the generation of haptic playback by streaming the digital waveform data or transmitting the digital waveform data in groups for more bandwidth efficiency. Waveforms can be generated by reading data from the FIFO at various sampling rates.

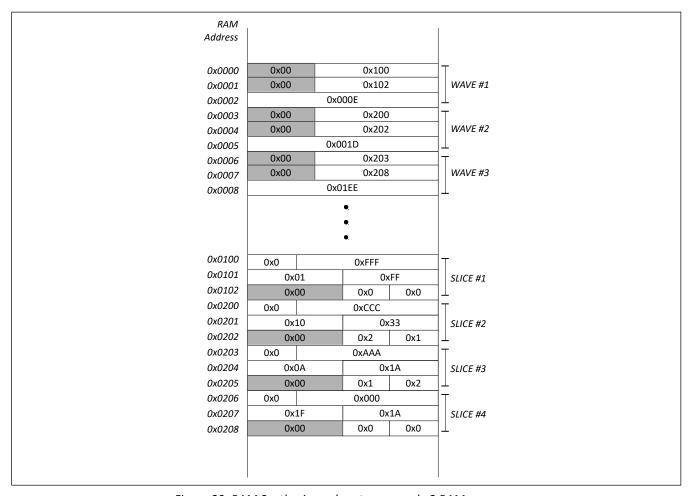

The BOS1921/BOS1931 integrates a Waveform Synthesizer (WFS) and a 2 kB on-chip 1024×16 RAM that enable haptic waveform generation using RAM Playback mode and RAM Synthesis mode. The WFS allows the generation of customized continuous haptic waveforms with minimal intervention by the host MCU.

The BOS1921 features an advanced sensing interface that allows mechanical buttons to be replaced with an enhanced user interface. Piezo actuator press/release trigger conditions allow the detection of an interaction with a piezo actuator and automatically trigger haptic waveform feedback within 30  $\mu$ s. A GPIO pin can be used as an interrupt to indicate the MCU that a sensing voltage event has occurred or a change in the device state.

The BOS1921/BOS1931 can use any commercial off-the-shelf (COTS) inductor. The inductor value can be chosen to optimize the power, size or performance depending on the user's application. With a start-up time of less than 300  $\mu$ s from its low-power mode, the device can be used in applications requiring low latency.

### **6.2 Features**

#### 6.2.1 Digital Front-End Interface

The BOS1921/BOS1931 uses an I3C target interface supporting SDR communication up to 12.5 Mbps. This high-speed communication interface enables multiple ICs to share a common communication bus. Its digital front-end enables waveform data to be stored in memory. The digital interface also provides access to internal registers which control the BOS1921/BOS1931 operation and performance, see section 6.3 for more details.

#### 6.2.2 GPIO

A General-Purpose Input / Output (GPIO) pin in the VDDIO domain is available and supports an open-drain (default) or push-pull configuration. The GPIO is active-low and can be used as an interrupt to notify the host MCU of various events such as sense voltage events or an error. The GPIO can also be used as an input to trigger a predefined haptic waveform output.

The GPIO pin can be configured with the following register bits:

- COMM.GPIODIR is used to set the GPIO pin as input or output.

- COMM.GPIOSEL[2:0] is used to select the signal that is output to the GPIO pin.

- COMM.OD is used to set the GPIO pin to push-pull or open-drain configuration.

#### 6.2.3 Flexible Waveform Generation

The output waveform voltage range can be selected between ±95 V and ±13.25 V as detailed in Table 9.

Table 9: Output Voltage Ranges List

| REGISTER     | REGISTER VALUE | OUTPUT RANGE (V) | OUTPUT RESOLUTION (V) |

|--------------|----------------|------------------|-----------------------|

| CONFIG.GAIND | 0x1            | ±13.25           | 0.0076                |

| CONFIG.GAIND | 0x0            | ±95              | 0.0545                |

#### 6.2.3.1 Direct Mode

With <u>PLAY MODE[1:0]</u> bits set to 0x0, the haptic waveform samples are played as they are sent from the host MCU to the RAM using <u>REFERENCE</u> register. The rate at which the RAM data is read to generate the haptic waveform is set by <u>PLAY SRATE[2:0]</u> bits. See section 6.5 for details.

#### **6.2.3.2 FIFO Mode**

The digital front-end gives access to RAM as a 1024-sample FIFO for waveform playback with <u>PLAY MODE[1:0]</u> bits set to 0x1. FIFO entries are appended every time waveform samples are written in the <u>REFERENCE</u> register. Digital samples are represented as 12-bit unsigned values. If <u>OE</u> bit is set to 0x1, the FIFO entries are read automatically out of the FIFO at a rate set by <u>PLAY SRATE[2:0]</u> bits. See section 6.6 for details.

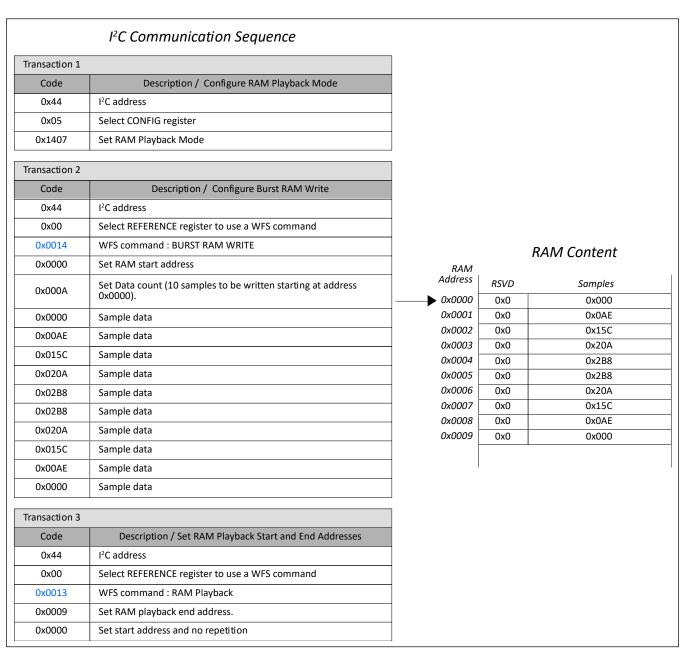

### 6.2.3.3 RAM Playback Mode

RAM Playback mode is selected with <u>PLAY MODE[1:0]</u> bits set to 0x2. In RAM Playback mode, on-chip RAM of 2 kB is used to store arbitrary haptic waveforms as waveform amplitude samples in 12-bit unsigned format. The waveform is sampled at a rate set by <u>PLAY SRATE[2:0]</u> bits. See section 6.7 for more details.

#### 6.2.3.4 RAM Synthesis Mode

RAM Synthesis mode is selected with bits <u>PLAY MODE[1:0]</u> set to 0x3. With this mode, the BOS1921/BOS1931 uses the Waveform Synthesizer (WFS) to generate waveforms using parameters stored in the 2 kB RAM. RAM Synthesis mode allows generation of sine waveforms of various amplitudes and frequencies without having to send every sample of the waveform to RAM as is the case with RAM Playback mode. This allows complex waveforms to be produced with minimal data communication. See section 6.8 for details.

#### 6.2.4 Piezo Sensing (BOS1921 Only)

The BOS1921 can use a piezo actuator as a force sensor by measuring the voltage across its terminals.

The BOS1921 also features an embedded sensing comparator that can be configured to automatically trigger an already programmed waveform.

The GPIO pin can inform the MCU that a sensing voltage event occurred or a triggered waveform has finished playing using <a href="GPIOSEL[2:0]">GPIOSEL[2:0]</a> bits. Voltage sensed is available with <a href="SENSE VALUE[11:0]">SENSE VALUE[11:0]</a> bits, which can be read at any time when sensing is activated (<a href="CONFIG.SENSE">CONFIG.SENSE</a> bit set to 0x1) and is useful for MCU-based customized sensing algorithms. See section 6.4 for more detail.

The sensing resolution can be selected between 7.6 mV and 54.5 mV as detailed in Table 10.

#### **Product Datasheet**

Table 10: Sensing Ranges List

| REGISTER            | REGISTER VALUE | INPUT RANGE (V) | SENSING RESOLUTION (V) |

|---------------------|----------------|-----------------|------------------------|

| CONFIG.GAINS        | 0x1            | ±13.25          | 0.0076                 |

| <u>CONFIG.GAINS</u> | 0x0            | ±95             | 0.0545                 |

#### 6.2.5 Continuous Mode

With RAM Synthesis or RAM Playback mode, it is possible to play a waveform for an indefinite amount of time without the intervention of an external MCU. This feature is well suited for cooling or micropump applications that need to operate for long periods of time while minimizing overall system power and resource usage.

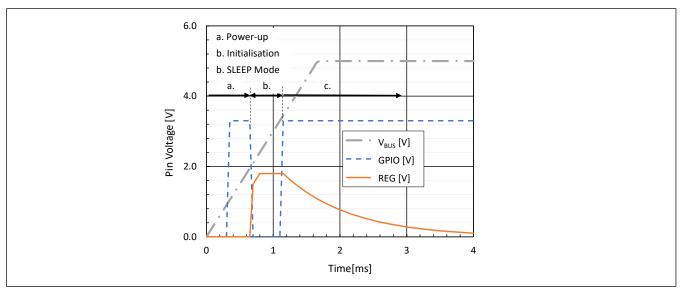

#### 6.2.6 SLEEP Mode

When no output waveform is being requested, no sensing is needed (BOS1921 only) and the output is disabled (bit <u>OE</u> set to 0x0), the device can enter in one of its two low-power modes by the use of the bit <u>DS</u>: IDLE or SLEEP mode. By default, power mode is IDLE (bit <u>DS</u> set to 0x0). SLEEP mode is selected when bit <u>DS</u> is set to 0x1.

In SLEEP mode, the BOS1921/BOS1931 preserve its RAM and the contents of the registers by default (RET bit set to 0x0). By setting RET bit set to 0x1, SLEEP mode does not preserve RAM and neither the contents of the registers to reduce the power consumption. Note that to reduce the total quiescent current of the device, the following should be done:

- Disabled state retention (set RET bit to 0x1)

- Power off VDDIO supply.

The BOS1921/BOS1931 wakes up from SLEEP mode when a communication occurs on its I<sup>2</sup>C/I3C interface (the data will not have any effect on the configuration of the registers).

#### 6.2.7 Low Latency Startup

The BOS1921/BOS1931 features a fast start-up time. From IDLE or SLEEP mode, the device takes less than 300  $\mu$ s to start playing the waveform. This makes the device a very small contributor to system latency.

#### 6.2.8 Device Reset

The BOS1921/BOS1931 device has software-based reset functionality. When <u>RST</u> bit is set to 0x1, all registers are set to their default value and IC goes in IDLE state. <u>RST</u> bit self-clears once the reset is complete.

The following sequence must be done to safely reset the device while playing a waveform in FIFO or Direct mode:

- 1. Set CONFIG.OE bit must be set to 0x0.

- 2. Wait for the device to be in IDLE by polling <a href="IC STATUS.STATE[1:0]">IC STATUS.STATE[1:0]</a> bits.

- 3. Reset the device by setting RST bit to 0x1.

## 6.2.9 Device Synchronization

Multiple BOS1921/BOS1931 devices can be synchronized using SYNC pin to play haptic waveforms simultaneously on their respective piezo actuator with a phase delay of less than 2 μs between them.

#### **Product Datasheet**

Synchronization is achieved by connecting the SYNC pin of all devices with each other. A 10 k $\Omega$  pull-up resistor is needed between SYNC node and  $V_{DDIO}$ . The sequence to use device synchronisation is the following:

- 1) Set OE bit and SENSE bit to 0x0 on all devices.

- 2) Set SYNC bit to 0x1 on all devices.

- 3) For Each devices set OE bit to 0x1. The devices will wait on each other before starting to play the waveform and will synchronize the haptic waveforms within less than 2 µs during playback.

Note that SYNC pin must be tied to ground if unused.

#### **6.2.10 Adjustable Current Limit**

The maximum current of the power converter must be limited to avoid damage to both the  $L_1$  inductor and the BOS1921/BOS1931 device by selecting the appropriate  $R_{\text{sense}}$  value (see section 7.5.3). The BOS1921/BOS1931 determine the current flowing through the  $L_1$  inductor by measuring the voltage drop across  $R_{\text{sense}}$ , which is positioned between the RP/VDD and RM pins.

The current limit flowing through SW pin should be selected based on the following:

- Ensure that the current is lower than the saturation limit of the inductor L1.

- Ensure that the current is high enough to allow sufficient energy transfer to and from the piezo actuator.

The solution should be tested during its worst-case operation to ensure that the BOS1921/BOS1931 meets the bandwidth requirement of the application.

#### 6.2.11 Internal Charge Pump

The BOS1921/BOS1931 has an internal 5 V charge pump which requires a 0.1  $\mu$ F capacitor ( $C_{PUMP}$ ) with a 6.3 V voltage rating or more to be connected on HV pin.

#### 6.2.12 Energy Recovery

The BOS1921/BOS1931 IC implements bidirectional power transfer: input to output, and output to input. Such architecture enables the recovery of the energy accumulated on the capacitive load and transfers it back to the input. The internal controller automatically determines the direction of the power flow during waveform playback.

#### 6.2.13 Unidirectional Power Input (UPI)

The BOS1921/BOS1931 can sink and source current from the power delivery network (PDN) during normal operation thanks to its energy recovery feature. If the PDN can't sink current (e.g., if the device is powered by batteries), the Unidirectional Power Input (UPI) must be configured by setting UPI bit to 0x1. UPI allows the device to appear as a resistive load to the power supply (the device only sinks current) and reducing RMS current flowing in the PDN. UPI does not affect the efficiency of the BOS1921/BOS1931, but it causes the following to happen:

- First, power is drawn from the input source when the amplitude of the output waveform increases.

- Second, energy recovered accumulates on the input capacitor (C<sub>VDD</sub>) when the amplitude of the output waveform decreases.

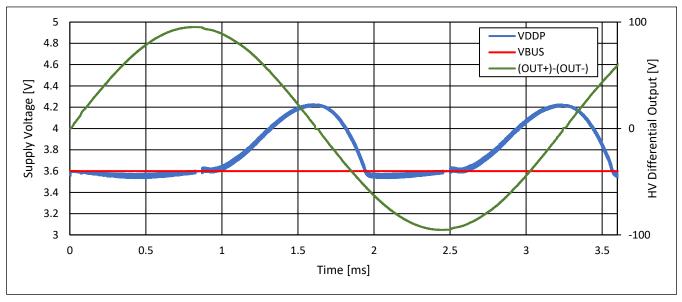

Energy accumulation on the  $C_{VDD}$  capacitor causes the voltage at VDDP pin to increase, as shown in Figure 16. The voltage increase can be adjusted by first calculating the maximum energy that may be recovered

from the load and then sizing  $C_{VDD}$  appropriately to achieve the desired voltage increase (see section 7.5.5). Voltage at VDDP pin should never exceed 5.5 V.

Figure 15: Block diagram of the Unidirectional Power Input (UPI)

Figure 16: Voltage increases at VDDP pin during energy recovery when bit  $\underline{UPI}$  is set to 0x1,  $C_{VDD} = 100 \ \mu F$ ,  $C_{Load} = 100 \ nF$

#### 6.2.14 Adjustable Internal Clock

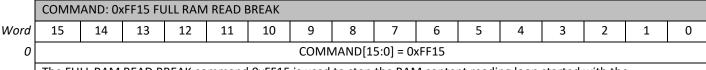

The internal clock oscillator frequency is trimmed during fabrication using hardware fuses. When initialized, the BOS1921/BOS1931 retrieves the hardware fuse values and push them to the TRIM block to adjust the oscillator frequency based on the fuse values (see Figure 34). The <u>TRIM</u> register allows modifying the TRIM values to adjust oscillator frequency.

The feature can be used to match the external system clock frequency with the BOS1921/BOS1931 internal clock frequency, which is used to determine the FIFO read-out rate. This might be needed to minimize waveform distortion if the user writes waveform data at a constant rate to the FIFO, without managing space available in it. To successfully adjust internal clock frequency, OE bit needs to be set to 0x0.

#### **Product Datasheet**

The internal oscillator can be adjusted with the following sequence:

- 1. Set CONFIG.OE bit to 0x0.

- 2. Set TRIM.TRIMRW[1:0] bits to one of the following values:

- a. Set to 0x1 to latch the Hardware Fuses to Trim Block and push them to the TRIM register, or

- b. Set to 0x2 to retrieve the oscillator trim value contained in the TRIM block and push the value to the TRIM register.

- 3. Wait 1 ms.

- 4. Read <u>TRIM.TRIM OSC[5:0]</u> bits (using bits <u>COMM.RDADDR[4:0]</u>) to get the internal oscillator trim value specific to the device.

- 5. In one transaction, set the TRIM register with the following field:

- a. TRIM OSC[5:0] bits set to the desired value.

- b. TRIMRW[1:0] bits set to 0x3 to write TRIM OSC[5:0] value to TRIM block.

The same procedure can be used to adjust the internal 1.8 V regulator voltage (pin REG) using bits <a href="https://doi.org/10.1016/j.com/ncs/">TRIM.TRIM REG[2:0] instead of TRIM.TRIM OSC[5:0] bits.</a>

#### 6.2.15 Fault and Warning Behaviour

This section lists the various faults detected by the device. Note that faults detected by the device may be caused by the following:

- Device operating outside of its safe operating conditions.

- Wrong component value (e.g., R<sub>sense</sub>, C<sub>HV</sub>, C<sub>VDD</sub> or L<sub>1</sub>).

- Noise induced by improper printed circuit board layout.

### 6.2.15.1 Overvoltage Fault

The overvoltage fault is triggered to prevent damage when voltage level on OUT+ or OUT- pin relative to  $V_{\text{BUS}}$  voltage is outside safe operating conditions. The fault is triggered in the following situations:

- When playing haptic waveforms with high gain in the following conditions:

- OE bit set to 0x1.

- SENSE bit set to 0x0.

- o GAIND bit set to 0x0.

- Voltage level on OUT+ pin relative to V<sub>BUS</sub> is above 100 V or voltage level on OUT- pin relative to V<sub>BUS</sub> is below -100 V.

- When playing haptic waveforms with low gain in the following conditions:

- OE bit set to 0x1.

- SENSE bit set to 0x0.

- o GAIND bit set to 0x1.

- Voltage level on OUT+ pin relative to V<sub>BUS</sub> is above 14 V or voltage level on OUT- pin relative to V<sub>BUS</sub> is below -14 V.

- When using piezo actuator sensing with the BOS1921 and high gain in the following conditions:

- OE bit set to 0x1.

- SENSE bit set to 0x1.

- o GAINS bit set to 0x0.

- Voltage level on OUT+ pin relative to V<sub>BUS</sub> is above 100 V or voltage level on OUT- pin relative to V<sub>BUS</sub> is below -100 V.

#### **Product Datasheet**

- When using piezo actuator sensing with the BOS1921 and low gain in the following conditions:

- o OE bit set to 0x1.

- SENSE bit set to 0x1.

- o GAINS bit set to 0x1.

- Voltage level on OUT+ pin relative to V<sub>BUS</sub> is above 14 V or voltage level on OUT- pin relative to V<sub>BUS</sub> is below -14 V.

If an overvoltage condition is detected during waveform generation, the following events occur:

- IC STATUS.OVV fault bit is set.

- IC STATUS.STATE[1:0] bits are changed to 0x3 (ERROR state).

- Output voltage ramp down to VDD.

The <u>OVV</u> bit will clear automatically and the BOS1921/BOS1931 state will change to IDLE (bits <u>STATE[1:0]</u> set to 0x0) with the following conditions:

- OE bit is 0x0.

- Output voltage is lower than the maximum allowed *V<sub>OUT(FS)</sub>*.

#### 6.2.15.2 Output Short Circuit Fault

The BOS1921/BOS1931 has an output short circuit protection to prevent excessive current to flow because of a shorted load. In case a short circuit is detected, the following events occur:

- IC STATUS.SC fault bit is set.

- IC STATUS.STATE[1:0] bits are changed to 0x3 (ERROR state).

- Output voltage ramp down to VDD.

The <u>SC</u> bit will clear automatically and the BOS1921/BOS1931 state will change to IDLE (bits <u>STATE[1:0]</u> is 0x0) with the following conditions:

- Bit OE is 0x0.

- Output voltage is lower than the maximum allowed V<sub>OUT(FS)</sub>.

#### 6.2.15.3 Over Temperature Fault

The BOS1921 has an internal temperature sensor that puts the BOS1921/BOS1931 in ERROR state in case the die junction temperature exceeds 145 °C. In this case, the following events occur:

- IC STATUS.OVT fault bit is set.

- IC STATUS.STATE[1:0] bits are changed to 0x3 (ERROR state).

- Output voltage ramp down to VDD.

The OVT bit will clear automatically and the BOS1921/BOS1931 state will change to IDLE (STATE [1:0] bits are 0x0) with the following conditions:

- OE bit is 0x0.

- Output voltage is lower than the maximum allowed V<sub>OUT(FS)</sub>.

The low power dissipation of the BOS1921/BOS1931 makes it unlikely that its temperature will reach 145 °C even when it is continuously operated at the maximum  $Z_L$  in the operating temperature range  $T_A$ .

#### 6.2.15.4 Under Voltage Fault

The BOS1921/BOS1931 monitor  $V_{BUS}$ , and if its voltage is below 2.875 V during waveform generation, the following events occur:

- IC STATUS.UVLO bit is set.

- IC STATUS.STATE[1:0] bits are changed to 0x3 (ERROR state).

- Output voltage ramp down to  $V_{DD}$ .

<u>UVLO</u> bit will self-clear and the BOS1921/BOS1931 state will change to IDLE (<u>STATE[1:0]</u> bits are set to 0x0) with the following conditions:

- OE bit is 0x0.

- Output voltage is lower than the maximum allowed V<sub>OUT(FS)</sub>.

#### 6.2.15.5 Current Detection Status Fault

For proper operation, the BOS1921 monitors the current using  $R_{sense}$  resistor connected to RP and RM pins. If no current is detected during waveform generation, the following event occurs:

- IC STATUS.IDAC fault bit is set.

- IC STATUS.STATE[1:0] bits are changed to 0x3 (ERROR state).

<u>IDAC</u> errors are typically triggered by incorrect component sizing (see section 7.5) or inadequate waveform data. If component sizing and waveform data are correct, see section 6.2.18 for details on other circumstances that can cause an IDAC error and strategies to avoid them.

To recover from an IDAC error, a software reset must be done using <u>CONFIG.RST</u> bit. <u>IC\_STATUS.IDAC</u> bit does not self-clear.

#### 6.2.15.6 Maximum Power Warning

During waveform playback, if the current in  $R_{sense}$  is equal or greater to the current limit defined in section 7.5.3, a maximum power warning is raised, and the following happens:

- IC STATUS.MXPWR warning bit is set.

- IC STATUS.STATE[1:0] bits remain 0x2 (RUN state).

- The waveform continues to play but is likely distorted.

<u>IC STATUS.MXPWR</u> bit does self-clears when the current in  $R_{sense}$  is lower than current limit defined in section 7.5.3.

#### 6.2.15.7 Brownout

The BOS1921/BOS1931 has internal brownout protections and if  $V_{REG}$  goes below 1 V. In this case, the following event occurs:

The chip issues a reset signal, and all registers are set to their default values.

When  $V_{REG}$  goes back to its specified operating voltage, the BOS1921/BOS1931 will be in IDLE state (STATE[1:0] bits set to 0x0).

#### 6.2.16 Output Timeout

Setting <u>TOUT</u> bit to 0x1 enables a timeout mechanism that forces the BOS1921 into SLEEP mode if no new communication has been received within 4 ms while playing a waveform in Direct or FIFO mode (<u>PLAY\_MODE[1:0]</u> bits set to 0x0 or 0x1).

Note that PLAY SRATE[2:0] bits are reset to 0x7 when the device enters SLEEP following a timeout event.

### **Product Datasheet**

More specifically, the BOS1921/BOS1931 enters SLEEP mode when the following conditions are met:

- COMM.TOUT bit is set to 0x1.

- <u>CONFIG.OE</u> bit is set to 0x1.

- PLAY MODE[1:0] bits are set to 0x0 or 0x1.

- The FIFO is empty when using FIFO mode (PLAY MODE[1:0] bits set to 0x1).

- The BOS1921/BOS1931 did not receive any communication on its digital interface for more than 4 ms.

#### 6.2.17 Interrupt

The BOS1921/BOS1931 features interrupt capabilities for different events enabled with the <u>INT\_ENABLE</u> register. The status of interrupts is read with the <u>INT\_STATUS</u> register.

The GPIO pin can be used to notify the MCU when one of the interrupts has occurred by setting <a href="GPIOSEL[2:0]">GPIOSEL[2:0]</a> bits set to 0x5.

There are up to 7 distinct interrupt events that can be configured. Each event can be enabled by programming the corresponding bit in the <u>INT\_ENABLE</u> register. A bit in the <u>INT\_STATUS</u> register is set when the condition corresponding to its event changes from *false* to *true* (i.e. rising edge condition).

All the <u>INT\_STATUS</u> register bits are automatically cleared in the following situations:

- INT STATUS register is read

- A soft reset is performed

- Device goes to SLEEP

The <u>INT\_STATUS</u> register bits are not cleared when setting its corresponding <u>INT\_ENABLE</u> register bits to 0x0.

Note that if the interrupt condition is already *true* when the interrupt is enabled, the interrupt can be immediately triggered and its corresponding <u>INT STATUS</u> register bits will be set to 0x1. It is thus recommended to clear any existing interrupt by reading <u>INT STATUS</u> register after enabling interrupts.

Note that the desired PLAY MODE bits should be set prior to configure interrupts.

The <u>INT\_ENABLE</u> register can be used to enable interrupts on the following events:

- <u>IE FHE</u> bit enables an interrupt when FIFO is at least half empty. Interrupt triggers when FIFO is more than half empty.

- <u>IE STCHG</u> bit enables an interrupt when the BOS1921/BOS1931 state change. Interrupt triggers when STATE[1:0] bits changed.

- <u>IE MXERR</u> bit enables an interrupt when there is a difference between the waveform played on the output and the setpoint.

- <u>IE SENSF</u> bit enables an interrupt when a sensing event occurred (BOS1921 only), i.e., it triggers when <u>SENS\_FLAG</u> bit is set to 0x1.

- <u>IE PLAY</u> bit enables an interrupt when the waveform playback status is set, i.e., it triggers when PLAYST bit is set to 0x1.

- <u>IE MAXP</u> enables an interrupt when a maximum power error occurred, i.e., it triggers when <u>MXPWR</u> bit is set to 0x1.

- <u>IE ERR</u> enables an interrupt when the BOS1921/BOS1931 state changes for ERROR, i.e., it triggers when STATE[1:0] bits are set to 0x3.

#### **Product Datasheet**

The following sequence presents an example on how to use the interrupt feature along with FIFO mode:

- 1. Set CONFIG.PLAY MODE[1:0] bits to 0x1 to select FIFO mode.

- 2. Set bit CONFIG.OE to 0x1 to enable the output.

- 3. Set INT ENABLE.IE FHE bit to 0x1 to enable the interrupt when the FIFO is half empty.

- 4. Set <u>COMM.RDADDR[4:0]</u> bits to 0x1F and read the <u>INT STATUS</u> register to clear existing interrupt.

- 5. Set GPIOSEL[2:0] bits to 0x5 to output the interrupt on the GPIO pin.

- 6. Set <u>COMM.RDADDR[4:0]</u> bits to 0x11, read <u>FIFO STATE</u> register and use <u>FIFO STATE.FIFO SPACE[9:0]</u> bits to determine space available in FIFO for new data.

- 7. Write as many 12-bit waveform data as possible according to space available in FIFO into the <a href="REFERENCE">REFERENCE</a> register.

- 8. Wait for a falling edge on the GPIO pin to occur, which indicates an interrupt occurred.

- 9. Set <u>COMM.RDADDR[4:0]</u> bits to 0x1F and read the <u>INT\_STATUS</u> register. The <u>INT\_STATUS.IS\_FHE</u> bit should be 0x1 and will be immediately cleared after reading register.

- 10. Repeat steps 5 to 8 until the desired waveform is completed.

#### 6.2.18 Output Bridge Protection

The BOS1921/BOS1931 includes a protection preventing the internal output bridge from changing polarity if a voltage greater than 4.4 V is present between the OUT+ and OUT- pins when playing a waveform. This protection is essential especially for BOS1921 when using sensing feature since the voltage on the piezoelectric ceramic terminal increases or decreases as it is deformed. Residual voltage can thus be present on the output of the BOS1921 when a waveform is requested to be played.

The bridge protection triggers in the following conditions:

- Play a positive haptic waveform when a negative voltage smaller than -4.4 V has built up on the piezoelectric ceramic.

- Play a negative haptic waveform when a positive voltage greater than 4.4 V has built up on the piezoelectric ceramic.

The bridge protection triggering causes a waveform played in the wrong polarity with or without IDAC error (see section 6.2.15.5). The bridge protection triggering can be caused by incorrect component sizing (see section 7.5) or inadequate waveform data.

To prevent the bridge protection to trigger, one could reset the voltage on the piezoelectric ceramic before starting to play the haptic waveform. This can be achieved by playing one of the following sets of data before the desired haptic waveform:

- Several 0 V data points.

- Voltage data points increasing from -2 V to 0 V if a positive waveform is intended to be played.

- Voltage data points decreasing from 2 V to 0 V if a if a negative waveform is intended to be played.

## 6.3 Digital Interface

A MIPI I3C target port enables communication with the BOS1921/BOS1931. I3C is backward compatible with legacy I<sup>2</sup>C devices, but I3C bus supports significantly higher speed. It is used to write data to the registers, whose content can also be read back.

#### 6.3.1 General Communication Protocol

The controller MCU can transfer data with the target BOS1921/BOS1931 using I3C or I<sup>2</sup>C standards.

### 6.3.1.1 Write Transactions

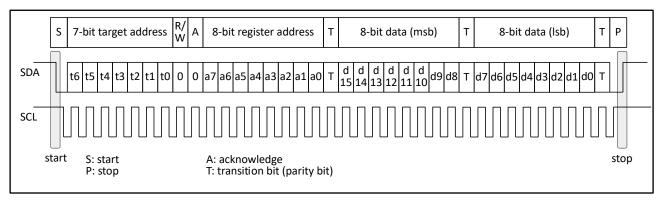

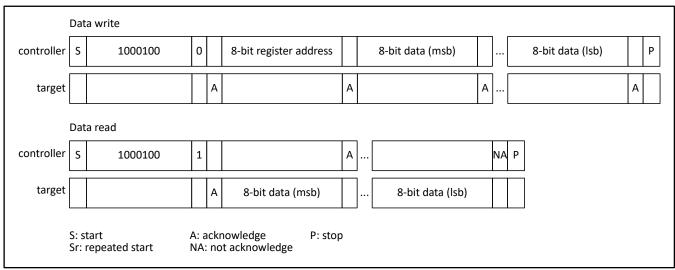

Both I<sup>2</sup>C and I3C can do write transactions with the following:

- The first byte contains the register address corresponding to the register to write to.

- Two bytes of register data; the first byte corresponds to the MSBs of the register data and the second byte corresponds to the LSBs of register data.

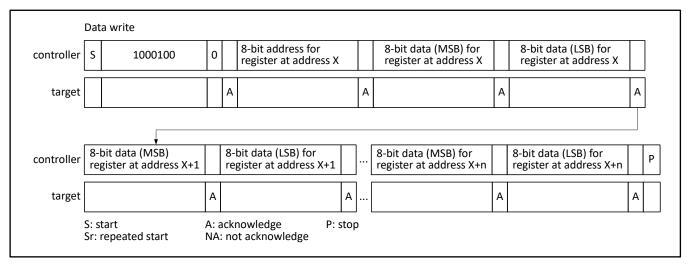

To write more than one register, three behaviours are possible:

- Register address = 0x00: All subsequent 2-byte words will automatically be written to the <u>REFERENCE</u> register. The communication frame must be stopped from accessing the other registers.

- 2. <u>STR</u> bit set to 0x1: The register address other than 0x00 will automatically be incremented every two bytes to allow writing multiple registers in the same transmission frame and reduce the number of bits used in the communication. The communication frame must be stopped to skip the remaining register addresses.

- 3. <u>STR</u> bit set to 0x0: A byte of address for each target register must be sent (no automatic address incrementation).

#### 6.3.1.2 Read transactions

Each communication transaction returns two bytes of data corresponding to the value of the register whose address is specified in <a href="RDADDR[4:0]">RDADDR[4:0]</a>. Burst reads are not supported, i.e., it is not possible to read multiple registers in a single access. However, the <a href="RDADDR[4:0]">RDADDR[4:0]</a> bits can automatically be incremented by 1 after each read by setting <a href="RDADDR[4:0]">RDADDR[4:0]</a> bits once with the address of the first register to be read, then issuing a sequence of reading accesses to read a series of registers.

#### 6.3.2 I3C Interface

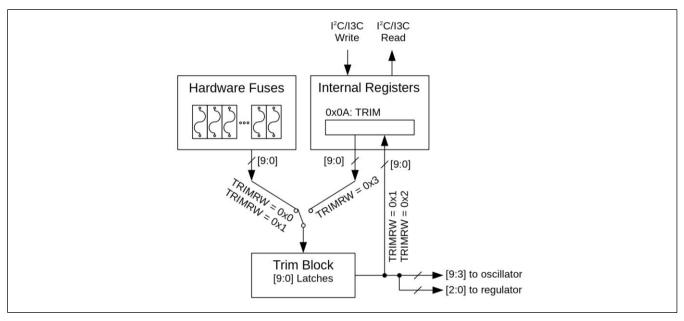

The I3C target functionality implemented in the BOS1921/BOS1931 is based on MIPI® Alliance Specification for I3C<sup>SM</sup>, version 1.1.1. I3C is a 2-wire bidirectional serial bus which always has one controller and one or more targets. The two wires are designated SDA and SCL: SDA is a bidirectional data signal, SCL is a clock signal. They connect respectively to BOS1921/BOS1931 SDA and SCL pins.

Table 11: Serial interface pin description

| PIN NAME | PIN DESCRIPTION           |

|----------|---------------------------|

| SDA      | Bidirectional Data Signal |

| SCL      | Controller Clock Signal   |

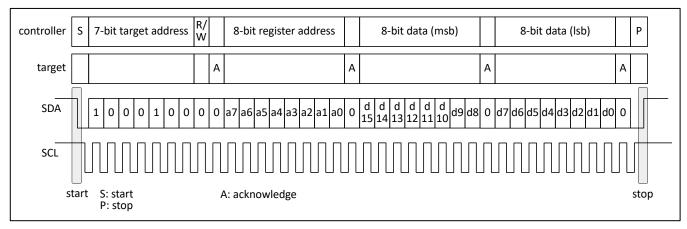

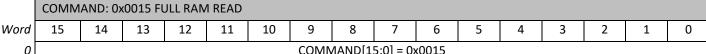

I3C communication is initiated by the controller which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. All I3C communication occurs within a frame. The basic frame begins with a START, followed by the header, the data, and a STOP (see Figure 17 for more details). The header following a START allows for bus arbitration. The controller uses the header to address target device(s). Each target is addressed by a unique 7-bit target address plus a read-write bit.

Figure 17: Typical I3C write communication frame

The I3C bus uses transitions on SDA while the clock is at logic high to indicate START and STOP conditions. A high-to-low transition on the SDA signal indicates a START, and a low-to-high transition indicates a STOP. All devices share the same SDA signals through a bidirectional bus using a wired-AND connection. The data transition on SDA must occur while the clock period is low.

The implemented I3C target of the BOS1921/BOS1931 has a legacy I<sup>2</sup>C default static address (7'h44). The 4 LSBs of the address can be changed by assigning the I2C\_ADDR bits. The BOS1921/BOS1931 will act as an I<sup>2</sup>C target using that address up until it is assigned a dynamic address. Once assigned a dynamic address, the BOS1921/BOS1931 will only operate as an I3C target until it is reset.

A 50 ns spike filter is included in the BOS1921/BOS1931. By default, the spike filter is active at power up. To operate in I3C, the user first needs to write to the broadcast address 0x7E at I<sup>2</sup>C speed. The filter will automatically be deactivated, and the user can then use I3C communication speed.

#### 6.3.2.1 I<sup>2</sup>C Communication

The BOS1921/BOS1931 acts by default as an I<sup>2</sup>C target using its static address (7'h44). Figure 18 shows a basic data-transfer sequence with I<sup>2</sup>C static addressing. Following a START, the controller generates the 7-bit target address and the read-write (R/W) bit to communicate with a target device. The target device then holds the SDA signal low during the next clock period to indicate acknowledgment to the controller. When this acknowledgment occurs, the controller transmits the next byte(s) of the sequence.

There are two addresses used to access a register. The first is the target address used to select the BOS1921/BOS1931. The second address is an 8-bit register address sent in the first byte transferred in a write operation. The register address points to a specific register (section 6.10). Automatic increments of address pointer can be set using STR bit. The address pointer is automatically incremented every two bytes, allowing continuous write operations.

Figure 18: Basic data transfer write sequence with I<sup>2</sup>C static addressing

Figure 19 presents a typical communication sequence in I<sup>2</sup>C. MSB is always sent first.

A typical write sequence from power up is the following:

- 1. Write with static address 0x44 with dummy data to wake-up the device.

- 2. Configure registers as needed.

Figure 20 presents a single communication transaction to access several main registers using <u>STR</u> bit set to 0x1 to access several main registers.

A 50 ns spike filter is included and activated at power up.

Figure 19: Typical data-transfer sequences with I<sup>2</sup>C static addressing

Figure 20: Typical data-transfer sequences with I<sup>2</sup>C static addressing with <u>STR</u> bit set to 0x1

### 6.3.2.2 I3C Communication

BOS1921/BOS1931 I3C interface is compliant with MIPI® Alliance Specification for I3C<sup>SM</sup>, version 1.1.1 and features the following:

- 1. Target only

- 2. SDR (Single Data RATE) up to 12.5 MHz

- 3. I<sup>2</sup>C compatibility with static address: 7'h44

- 4. Supports basic Common Command Codes (CCC) (see Table 12 for more details)

- 5. Does not support Hot Join (HJM)

- 6. Does not support In-Band Interrupt (IBI)

- 7. Provisional ID = 0x08A207814000 (see Table 13 or more details)

- 8. Bus Characteristic Register = 0x00

- 9. Device Characteristic Register = 0x25

Table 12: Common Command Codes (CCC) support

| COMMAND NAME | ТҮРЕ      | CODE | DESCRIPTION                      |

|--------------|-----------|------|----------------------------------|

| ENEC         | Broadcast | 0x00 | Enable events command            |

| DISEC        | Broadcast | 0x01 | Disable events command           |

| ENTAS0       | Broadcast | 0x02 | Enter activity state 0           |

| ENTAS1       | Broadcast | 0x03 | Enter activity state 1           |

| ENTAS2       | Broadcast | 0x04 | Enter activity state 2           |

| ENTAS3       | Broadcast | 0x05 | Enter activity state 3           |

| RSTDAA       | Broadcast | 0x06 | Reset dynamic address assignment |

| ENTDAA       | Broadcast | 0x07 | Enter dynamic address assignment |

| ENEC         | Direct    | 0x80 | Enable events command            |

| DISEC        | Direct    | 0x81 | Disable events command           |

| ENTAS0       | Direct    | 0x82 | Enter activity state 0           |

| ENTAS1       | Direct    | 0x83 | Enter activity state 1           |

#### **Product Datasheet**

| COMMAND NAME | TYPE   | CODE | DESCRIPTION                         |

|--------------|--------|------|-------------------------------------|

| ENTAS2       | Direct | 0x84 | Enter activity state 2              |

| ENTAS3       | Direct | 0x85 | Enter activity state 3              |

| RSTDAA       | Direct | 0x86 | Reset dynamic address assignment    |

| SETNEWDA     | Direct | 0x88 | Set new dynamic address             |

| GETPID       | Direct | 0x8D | Get provisional ID                  |

| GETBCR       | Direct | 0x8E | Get bus characteristics register    |

| GETDCR       | Direct | 0x8F | Get device characteristics register |

| GETSTATUS    | Direct | 0x90 | Get device status                   |

| GETCAPS      | Direct | 0x95 | Get HDR Capability                  |

Table 13: Defaults provisional ID details

| FIELD                    | WIDTH | VALUE               |  |

|--------------------------|-------|---------------------|--|

| Provisional ID (default) | 48    | 0x08A207814000      |  |

| Manufacturer ID          | 15    | 0x0451              |  |

| Part ID                  | 16    | 0x0781              |  |

| Instance ID              | 4     | 0x4 (I2C_ADDR[3:0]) |  |

| Vendor Defined           | 12    | 0x000               |  |

The BOS1921/BOS1931 will operate as an I3C target only after it is assigned a dynamic address by the controller using command ENTDAA with I<sup>2</sup>C timing constraints. A dummy write to address 0x7E can be performed prior to ENTDAA command to clear the 50 ns spike filter and enable communication at I3C speed without I<sup>2</sup>C constraints. A typical write sequence from devices power up is the following:

- 1. Send start condition with broadcast address 0x7E at I<sup>2</sup>C speed to clear I<sup>2</sup>C spike filter.

- 2. Send ENTDAA command.

- 3. Wake-up the chip with a dummy write.

- 4. Configure registers as needed.

## 6.3.3 Resolving I<sup>2</sup>C/I3C Address Conflicts

It is possible to connect multiple BOS1921/BOS1931 on the same I<sup>2</sup>C or I3C bus. By default, they all have the same address, so they all respond simultaneously to the same commands. However, it is possible to assign different addresses to each IC to allow accessing each one individually. The process requires to first configure the GPIO as a "Chip Select" before setting the I2C\_ADDR[3:0] bits. The procedure is the same for I<sup>2</sup>C or I3C protocols, but I3C mode requires the additional steps of resetting and reassigning the dynamic address after having set I2C\_ADDR[3:0] bits (see section 6.3.2.2).

#### **Product Datasheet**

The steps to reassign the I<sup>2</sup>C target address are the following:

- 1. Set the COMM.GPIODIR bit to 0x1 bit to use the GPIO as an input.

- 2. Apply a logic level low on the target device GPIO pin.

- 3. Set the <u>SUP\_RISE.I2C\_ADDR[3:0]</u> bits with the desired target device address. The new address will take effect immediately.

- 4. Wait at least 1  $\mu$ s after the completion of the I<sup>2</sup>C access performed during the previous step, after which the GPIO pin no longer needs to be used to access to the target device.

- 5. Using the new I<sup>2</sup>C address, perform a register access to make sure that the address change was successful.

Note that in I3C Mode the <u>SUP\_RISE.I2C\_ADDR[3:0]</u> bits are used to set the 4-bit Instance ID (i.e., bits [15:12] of the Provisional ID, see Table 13).

## 6.4 Piezo Actuator Sensing (BOS1921 Only)

The BOS1921 can sense the voltage across a piezo actuator and use it as a force sensor. The sensed voltage can be read to implement a custom detection algorithm.

The device can also be configured to generate an event when a sensing voltage threshold has been crossed. The sensed voltage event can result in the following:

- 1. Sense Voltage Alert: alert a MCU of the sensed voltage event.

- 2. Sense Voltage Trigger for Automatic Haptic Playback: The communication frame must be stopped to access other registers.

The following notes apply to the piezo actuator sensing feature:

- The <u>CONFIG.SENSE</u> bit activates the sensing of the actuator voltage without forcing a voltage on OUT+ and OUT- pins. This bit allows the piezo actuator voltage to vary freely as the user physically interacts with it.

- The <u>CONFIG.OE</u> bit enables the measurement of the HV pin voltage by the device, which is required for sensing feature to work.

- No haptic waveform should be playing while setting <u>CONFIG.SENSE</u> bit to 0x1. Wait until the IC <u>STATUS.PLAYST</u> bit is 0x1 before setting <u>CONFIG.SENSE</u> bit to 0x1.

- When sensing is activated, no haptic waveform can be output.

- One can activate piezo actuator sensing feature after playing a haptic waveform by simply setting the CONFIG.SENSE bit to 0x1 (no need to reset the CONFIG.OE bit to 0x0 and set it back to 0x1).

- To stop the sensing feature, it is recommended to reset the device using <u>RST</u> bit to reset registers and RAM.

#### 6.4.1 Sensed Voltage Reading

The sensed voltage can be read at any time to implement more complex sensing algorithms running in a MCU such as slope detection or voltage profile pattern recognition.

When sensing is activated, sensed voltage is continually updated and pushed to the <u>SENSE VALUE</u> register so the latest value can be read at any time. There is no required reading rate.

Note that <u>SENSE\_VALUE[11:0]</u> bits set to 0x0 means that the differential voltage is 0 V. However, when the circuit is in sensing and no signal is generated by a piezo actuator, a negative differential voltage of approximately -350 mV is read.

#### **Product Datasheet**

The following bits of the SENSE VALUE register are used to read sensed voltage:

- <u>SENSE VALUE[11:0]</u> bits are the 12-bit signed representation of the sensed voltage.

- <u>SENSE</u> bit indicates if sensing mode is activated.

## 6.4.1.1 Polling Sequence Example

A typical communication sequence to poll the sensed voltage is as follows:

- 1. Set CONFIG.ONCOMP to 0x0 to prevent sensed voltage from triggering a sensing event.

- 2. Set **CONFIG.SENSE** to 0x1 to enable piezo actuator sensing.

- 3. Set CONFIG.OE to 0x1 to start sensing.

- 4. Read SENSE VALUE[11:0] bits.

- 5. Repeat the step 4) as needed.

## **6.4.2 Sense Voltage Alert**

An internal sensing comparator allows to detect when the sensed voltage on the piezo actuator crosses a configurable threshold voltage. When the detection conditions are met, the <u>SENSE\_FLAG</u> bit is set to 0x1. The SENSE\_FLAG bit can be reset by reset <u>ONCOMP</u> bit to 0x0.

The sensing voltage alert settings are the following:

- <u>CONFIG.ONCOMP</u> bit enables the embedded comparator which triggers the alert. It must be set to 0x1 to enable comparison.

- <u>SENSING.SIGN</u> defines whether the voltage feedback value must be above or below the threshold for the detection to succeed.

- <u>SENSING.REP[2:0]</u> bits define how long the voltage must be above or below the threshold for detection to succeed (hold time).

- <u>SENSING.STHRESH[11:0]</u> bits define a differential voltage threshold to be crossed for the detection to succeed.

- SENSE VALUE.SENSE FLAG bit indicates when a detection has occurred.

- <u>COMM.GPIOSEL[2:0]</u> bits set to 0x6 configure the GPIO pin to indicate when a sense voltage alert

has occurred (note that the interrupt mechanism can also be used by setting <u>GPIOSEL[2:0]</u> to

0x5).

#### 6.4.3 Sense Voltage Trigger for Automatic Haptic Playback

The BOS1921 can detect force on the piezo actuator and automatically play a pre-programmed waveform using FIFO (section 6.6), RAM Playback (section 6.7) or RAM Synthesis (section 6.8) modes with minimal intervention needed by the MCU.

GPIO pin can notify the MCU that the waveform playback is completed.

#### **Product Datasheet**

The following is used to enable and monitor Automatic Haptic Playback:

- A waveform must be armed (see section 6.8.7 for an example). The waveform must be armed again each time an automatic waveform playback occurs.

- <u>CONFIG.SENSE</u> bit enables piezo actuator sensing. The bit self-clears and must be enabled again each time an automatic waveform playback occurs.

- <u>CONFIG.ONCOMP</u> bit enables the embedded comparator which triggers the automatic waveform playback. <u>ONCOMP</u> bit must be disabled and then enabled again each time an automatic waveform playback occurs.

- <u>CONFIG.AUTO</u> bit enable Automatic Haptic Playback. The bit self-clears and must be enabled again each time an automatic waveform playback occurs.

- SENSE VALUE.SENSE FLAG bit indicates when a detection has occurred.

- IC STATUS.PLAYST bit indicates when waveform playback has finished.

- <u>COMM.GPIOSEL[2:0]</u> bits set to 0x6 configure the GPIO pin to notify that a sense voltage event has occurred. Note that the interrupt mechanism can also be used by setting <u>GPIOSEL[2:0]</u> to 0x5.

#### 6.4.3.1 Sequence Example for Button Press Sensing with Automatic Playback

A typical communication sequence to configure a press button Automatic Haptic Playback is as follows:

- 1. Program waveform using RAM Playback (section 6.5) or RAM Synthesis (section 6.8) mode.

- 2. Set <a href="COMM.GPIOSEL[2:0">COMM.GPIOSEL[2:0]</a> to 0x6 to be notified on the GPIO pin that a sense voltage event has occurred.

- 3. Set SENSING.REP[2:0] to 0x5 to set 2048 µs hold time.

- 4. Set SENSING.THRESH[11:0] to 0x7 to set 750 mV threshold.

- 5. Set <u>SENSING.SIGN</u> bit to 0x0 to trigger on a voltage above the threshold (detect an increasing voltage).

- 6. Set <u>CONFIG.AUTO</u> bit to 0x1 to play a pre-programmed RAM Playback or RAM Synthesis waveform automatically on a successful detection.

- 7. Set CONFIG.ONCOMP bit to 0x1 to enable the embedded sensing comparator.

- 8. Set CONFIG.SENSE bit to 0x1 to enable piezo actuator sensing.

- 9. Set **CONFIG.OE** bit to 0x1 to start sensing.

Note that all bits in CONFIG register may be set in the same I<sup>2</sup>C/I3C instruction.

#### 6.4.3.2 Sequence Example for Button Release Sensing with Automatic Playback

Once a detection occurred, sensing can be set again for a release button Automatic Playback using a communication sequence as follows:

- 1. Set <u>CONFIG.ONCOMP</u> bit to 0x0 to reset the sensing comparator.

- 2. Arm the next waveform depending on playback mode used as follows:

- a. RAM Playback: issue an RAM PLAYBACK WFS command.

- b. RAM Synthesis: issue an RAM Synthesis WFS command

- 3. Set <u>SENSING.REP[2:0]</u> to 0x5 to set 2048 µs hold time.

- 4. Set SENSING.THRESH[11:0] bits to 0xFFE to set -200mV threshold.

- 5. Set <u>CONFIG.SIGN</u> to 0x1 to trigger a haptic playback on voltage below the threshold (detect a decreasing voltage).

- 6. Set **CONFIG.ONCOMP** to 0x1 to enable the sensing comparator.

- 7. Set <u>CONFIG.SENSE</u> bit to 0x1 to enable piezo actuator sensing.

- 8. Set <u>CONFIG.AUTO</u> bit to 0x1 to play a pre-programmed RAM Playback or RAM Synthesis waveform automatically on a successful detection.

- 9. Set CONFIG.OE to 0x1 to start sensing.

Note that all bits in **CONFIG** register may be set in the same I<sup>2</sup>C/I3C instruction.

#### 6.5 Direct Mode

In Direct mode (<u>PLAY MODE[1:0]</u> bits set to 0x0), the haptic waveform samples are played as they are sent from the host MCU to the <u>REFERENCE</u> register. The rate at which the data is read to generate the haptic waveform is set by <u>PLAY SRATE[2:0]</u> bits. An interpolation is done between user samples to generate the output waveform when <u>PLAY SRATE[2:0]</u> bits are 0x1 to 0x7.

Data management and synchronization can be facilitated by setting <u>GPIOSEL[2:0]</u> bit to 0x5 and <u>IE\_PLAY</u> to 0x1 to allow the corresponding GPIO to generate an interruption that notifies the MCU when the BOS1921/BOS1931 is ready to receive the next sample. Interpolation between user samples is done to generate the output waveform.

In Direct mode, the RAM is not used, and its content previously written using RAM Playback mode (section 6.7) or RAM Synthesis mode (section 6.8) is preserved.

Note that waveforms should begin and end with 0 V amplitude.

#### **6.5.1 Typical Operation Sequence**

The following sequence shows how to use Direct mode to play haptic waveforms:

- 1. Set COMM.GPIOSEL[2:0] bits to 0x1 to monitor when one more sample is ready to be sent.

- 2. Set <u>CONFIG.PLAY MODE[1:0]</u> bits to 0x0 to select Direct mode.

- 3. Set <u>CONFIG.OE</u> bit to 0x1 to enable output.

- 4. Write a waveform sample to the REFERENCE[11:0] bits.

- 5. On a GPIO pin falling edge, go to step 4. to send the next waveform sample to the device.

- 6. Set <a href="CONFIG.OE">CONFIG.OE</a> bit to 0x0 once the desired waveform is completed.

#### 6.6 FIFO Mode

In FIFO mode, the device uses RAM to implement a 1024-sample FIFO. The FIFO entries are appended every time waveform data is written in the <u>REFERENCE</u> register. When output is enabled, the FIFO entries are read automatically out of the FIFO at a rate set by <u>PLAY\_SRATE[2:0]</u> bits to output a haptic waveform. An interpolation is done between user samples to generate the output waveform when <u>PLAY\_SRATE[2:0]</u> bits are 0x1 to 0x7.

## Note the following:

- For waveform playback streaming, the FIFO data write rate must match the readout rate of the

waveform playback set by <u>PLAY\_SRATE[2:0]</u> bits to always keep valid data inside the FIFO. The

<u>PLAYST</u> bit is set to 0x1 when the FIFO becomes empty, causing the FIFO to hold the last valid

data and keep the output waveform in a steady state.

- Burst data transfers can be used to minimize the communication interface usage. Packets of 16-bit words can be sent in the same data payload to be written in the FIFO. The <u>FULL</u> bit is set when the FIFO becomes full and cannot accept more data. The <u>FIFO SPACE[9:0]</u> bits can be read to check available space before sending new data.

- In case OE bit is set to 0x0 during waveform playback, the waveform will continue to play until the FIFO is empty.

- When the FIFO is empty, the last FIFO entry will remain on the device output.

- It is recommended to start and end waveforms with 0 V.

- It is recommended to terminate waveforms with 0 V before setting the OE bit to 0x0, otherwise the output voltage will slowly decrease to 0 V.

#### 6.6.1 FIFO Depth

FIFO mode uses the RAM to implement the FIFO. Using FIFO mode with the default FIFO depth of 1024 locations could overwrite any waveform previously programmed using RAM Playback and RAM Synthesis modes.

FIFO mode can be used jointly with either RAM Synthesis or RAM Playback mode by configuring the FIFO dimension with a smaller number of RAM locations using the FIFO DEPTH command.

## **6.6.2 Typical Operation Sequence**

The following sequence shows how to use FIFO mode to play haptic waveforms:

- 1. Set CONFIG.PLAY MODE[1:0] bits to 0x1 to select FIFO mode.

- 2. Set <u>CONFIG.OE</u> bit to 0x1 to enable the output.

- 3. Set <u>COMM.RDADDR[4:0]</u> bits to 0x11 and read <u>FIFO\_STATE</u> register.

- a. If FIFO STATE.FULL bit is 0x1 skip to step 5.

- b. If <u>FIFO STATE.FULL</u> bit is 0x0, use <u>FIFO STATE.FIFO SPACE[9:0]</u> bits to determine space available in FIFO for new data.

- 4. Write as many 12-bit waveform data as possible according to space available in FIFO into the REFERENCE register.

- 5. Repeat steps 3 and 4 until the desired waveform is completed.

- 6. Set CONFIG.OE bit to 0x0 once the desired waveform is completed.

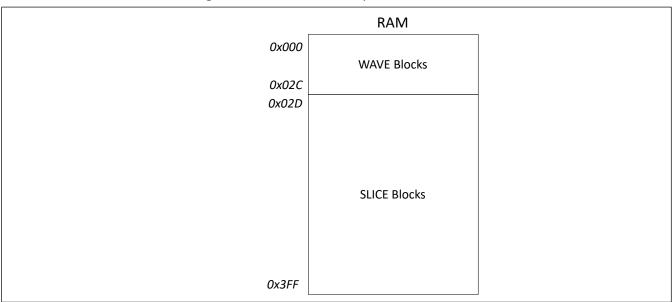

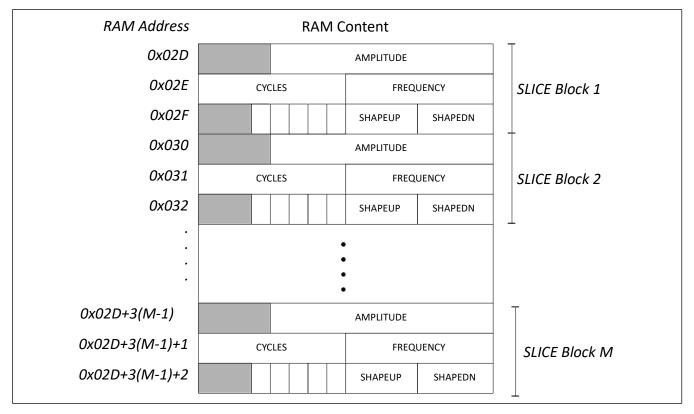

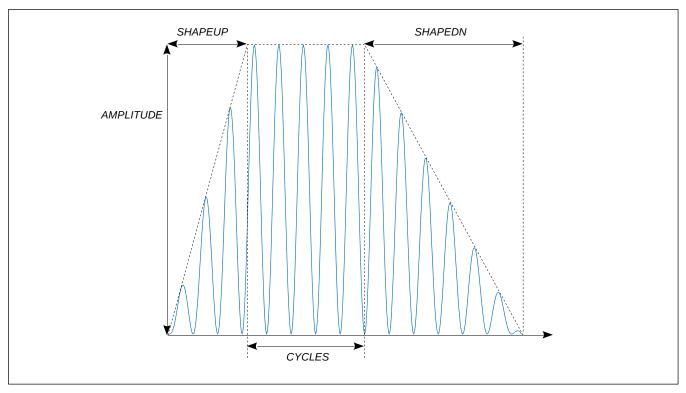

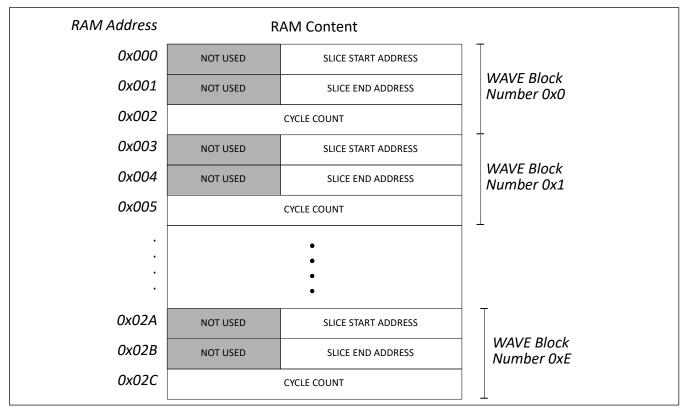

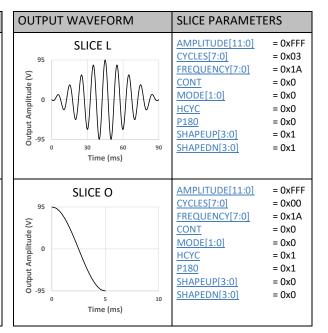

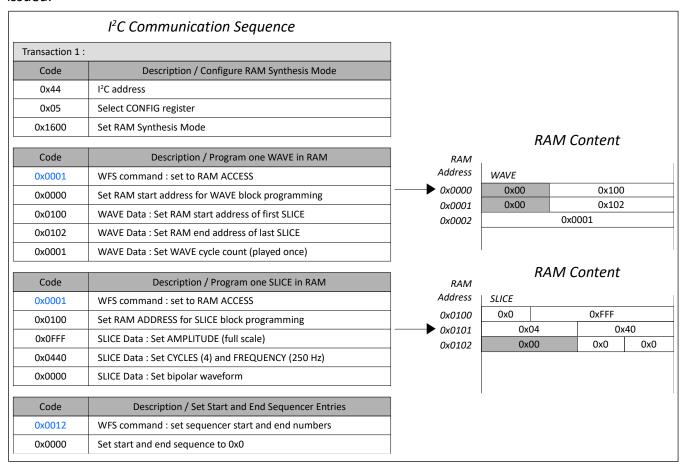

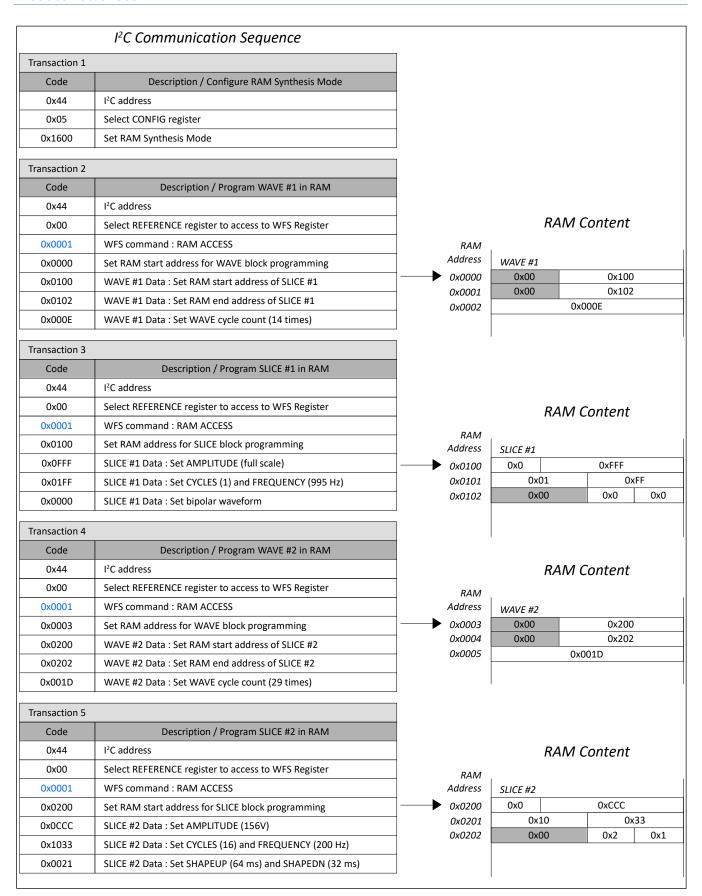

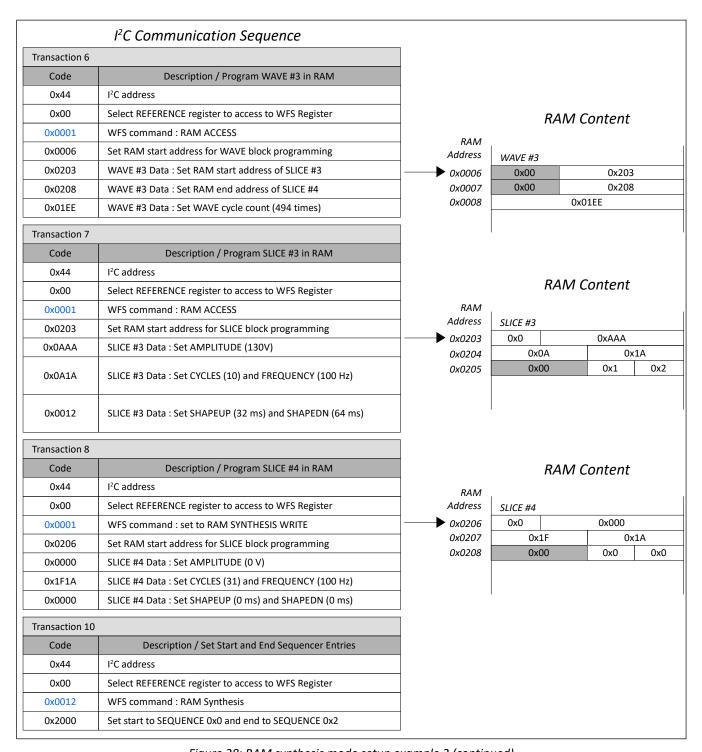

#### **Product Datasheet**